## **APPLICATION NOTE**

### **Application Hints for ATA5723/ATA5724/ATA5728**

#### ATA5723/ATA5724/ATA5728

#### Introduction

The UHF receiver ATA5723, ATA5724, and ATA5728 are designed specially for automotive application like Remote Keyless Entry as well as Tire Pressure Monitoring System. These receivers are upgrades of ATA5743 and ATA5760. They have compatible pinning that allows the development of one layout for applications in three different ISM (industrial Scientific Medical) frequency bands. The frequency ranges are 312.5MHz to 317.5MHz, 431.5MHz to 436.5MHz and 868MHz to 870MHz. Another benefit of the receiver is the reuse of the software from Atmel<sup>®</sup>'s older receiver, the ATA5743. Additional features include the RSSI output, the pierce crystal oscillator achieving a better oscillation margin, an improved sensitivity as well as the image rejection.

The purpose of this application note is to give a designer some hints how to start developing a receiver module with ATA5723/ATA5724/ATA5728.

# **Calculating the Required Crystal Frequency**

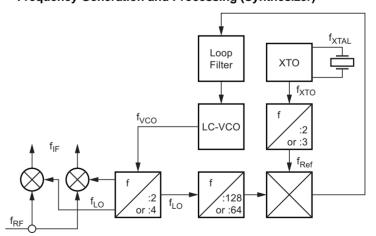

Figure 1. System Block Diagram for the Receivers Containing the Internal Frequency Generation and Processing (Synthesizer)

A reference frequency ( $f_{Ref}$ ) in the receiver is based on the crystal oscillator's frequency ( $f_{XTO}$ ), the loaded crystal resonance frequency ( $f_{XTAL}$ ) respectively. The defined reference frequency is:

For ATA5723:

$$f_{Ref} = \frac{f_{XTO}}{3}$$

Equation 1

For ATA5724:

$$f_{Ref} = \frac{f_{XTO}}{2}$$

Equation 2

For ATA5728:

$$f_{Ref} = \frac{f_{XTO}}{2}$$

Equation 3

The fixed intermediate frequencies (IF) for the receivers are:

IF of ATA5723 is 987kHz

IF of ATA5724 is 987kHz

IF of ATA5728 is 947.8kHz

The local oscillator frequency ( $f_{LO}$ ) can be calculated as:

$$f_{LO} = f_{RF} - f_{IF}$$

Equation 4

The correlation between local oscillator frequency (f<sub>LO</sub>) and the Voltage Oscillator frequency (f<sub>VCO</sub>) is:

For ATA5723:

$$f_{LO} = \frac{f_{VCO}}{4}$$

Equation 5

For ATA5724:

$$f_{LO} = \frac{f_{VCO}}{4}$$

Equation 6

For ATA5728:

$$f_{LO} = \frac{f_{VCO}}{2}$$

Equation 7

The reference frequency (f<sub>Ref</sub>) will be compared with the local oscillator frequency divided by a factor of 64 or 128.

For ATA5723:

$$f_{Ref} = \frac{f_{LO}}{64}$$

Equation 8

For ATA5724:

$$f_{Ref} = \frac{f_{LO}}{64}$$

Equation 9

For ATA5728:

$$f_{Ref} = \frac{f_{LO}}{128}$$

Equation 10

Using the aforementioned formulas, the crystal frequency for the receivers can be calculated as follows:

For ATA5723:

$$f_{XTAL} = \frac{(f_{RF} - f_{IF}) \times 3}{64}$$

Equation 11

For ATA5724:

$$f_{XTAL} = \frac{(f_{RF} - f_{IF}) \times 2}{64}$$

Equation 12

For ATA5728:

$$f_{XTAL} = \frac{(f_{RF} - f_{IF}) \times 2}{128}$$

Equation 13

#### Example:

1. For the 315 MHz receiving frequency (ATA5723) the crystal frequency required can be calculated as follows:

$$f_{RF} = 315MHz$$

$f_{IF} = 987kHz$

$$f_{XTAL} = \frac{(315MHz - 987kHz) \times 3}{64} = 14.71935938MHz$$

2. For the 433.92MHz receiving frequency (ATA5724) the crystal frequency required can be calculated as follows:

$$f_{RF} = 433.92MHz$$

$f_{IF} = 987kHz$

$$f_{XTAL} = \frac{(433.92MHz - 987kHz) \times 2}{64} = 13.52915625$$

3. For the 868.3MHz receiving frequency (ATA5728) the crystal frequency required can be calculated as follows:

$$f_{RF} = 868.3MHz$$

$f_{IF} = 947.8kHz$

$$f_{XTAL} = \frac{(868.3MHz - 947.8kHz) \times 2}{128} = 13.55237813MHz$$

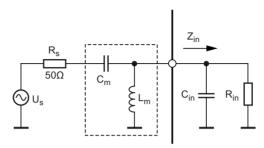

## 1. Matching the Receiver Input to the $50\Omega$

The input matching for the optimal sensitivity is matching to  $50\Omega$ . This can be achieved with the LC high-pass filter combination. Figure 1-1 shows an LC matching network, the equivalent circuit of the receiver's input and the  $50\Omega$  generator source. This section provides some mathematical correlations, which help to find the start values in the tuning of the matching values to  $50\Omega$  impedance. The determined start values are used for the matching of Atmel's development boards. The results of the demo boards' matching will be shown.

Figure 1-1. LC Matching Network to  $50\Omega$

The first important step is to find out the input impedance of the receivers and convert it into an equivalent parallel circuit. The input impedance of the receiver is listed below:

ATA5723

$$\rightarrow$$

Z<sub>in</sub> = 26.97 – j158.7 $\Omega$  at 315MHz

ATA5724

$$\rightarrow$$

Z<sub>in</sub> = 19.3 – j113.3 $\Omega$  at 433.92MHz

ATA5728

$$\rightarrow$$

Z<sub>in</sub> = 14.15 – j73.53 $\Omega$  at 868.3MHz

The admittance of the receiver (B<sub>in</sub>) can be estimated from the impedance Z<sub>in</sub>.

$$B_{in} = \frac{1}{Z_{in}}$$

Equation 14

The input resistance R<sub>in</sub> is:

$$R_{in} = \frac{1}{Re\{B_{in}\}}$$

Equation 15

Thus the reactance of the parallel input capacitance C<sub>in</sub> can be given as:

$$X_{in} = \frac{1}{Im\{B_{in}\}}$$

Equation 16

Using equation 17, the quality factor of the matching network (Q<sub>m</sub>) can be estimated.

$$Q_{\rm m} = \sqrt{\frac{R_{\rm in}}{R_{\rm s}} + 1}$$

Equation 17

The matching capacitance is derived from the reactance of the matching network and can be given as:

$$C_{\rm m} = \frac{1}{2\pi f X_{\rm m}}$$

Equation 18

The ideal inductor value can be calculated with equation 19:

$$L_{m} = \frac{X_{in} - X_{m}}{2\pi f(X_{in} + X_{m})}$$

Equation 19

From the equations 18 and 19 the start values of the matching elements for tuning purpose can be calculated:

ATA5723 at 315 MHz would be:  $L_m = 46.8 \text{nH} \ (\approx 47 \text{nH}); \ C_m = 2.36 \text{pF} \ (\approx 2.2 \text{pF})$

ATA5724 at 433.92 MHz would be:  $L_m$  = 25.9nH ( $\approx$ 27nH);  $C_m$  = 2.05pF ( $\approx$ 2pF)

ATA5728 at 868.3 MHz would be:  $L_m = 8.87$ nH ( $\approx 8.2$ nH);  $C_m = 1.38$ pF ( $\approx 1.5$ pF)

The optimal matching values after tuning are:

ATA5723 at 315MHz is:  $L_m$  = 39nH;  $C_m$  = 3pF ATA5724 at 433.92MHz is:  $L_m$  = 22nH;  $C_m$  = 2.2pF ATA5728 at 868.3MHz is:  $L_m$  = 5.6nH;  $C_m$  = 1.8pF

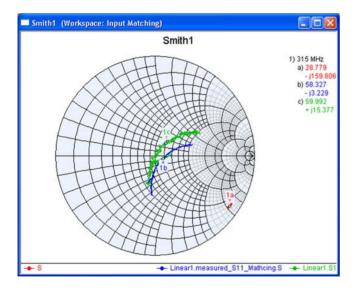

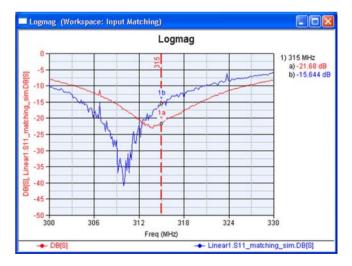

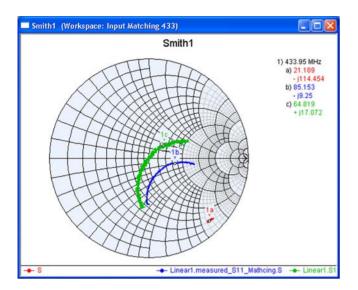

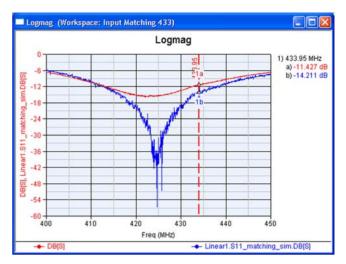

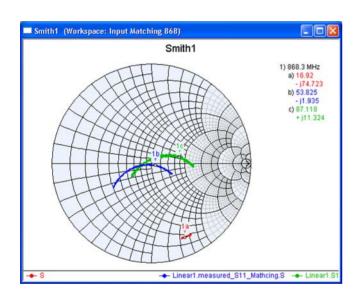

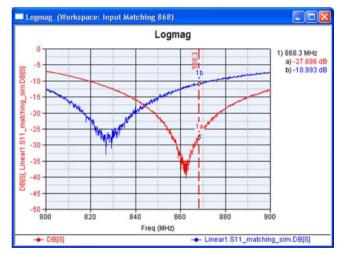

Figure 1-2, Figure 1-3 and Figure 1-4 show the input impedances of the receivers during the matching progress.

Note:

Smith chart:

- The red curve shows the input impedance without matching elements.

- The green curve illustrates the theoretical receiver input impedance with the determined start values for the tuning.

- The blue curve shows the measured input impedance after tuning progress.

#### Rectangular diagram:

- The blue curve illustrates the theoretical receiver input impedance with the determined start values for the tuning.

- The red curve shows the measured input impedance after tuning progress.

Figure 1-2. Input Impedance of ATA5723 before and after Matching

Figure 1-3. Input Impedance of ATA5724 before and after Matching

Figure 1-4. Input Impedance of ATA5728 before and after Matching

# 2. Development Board

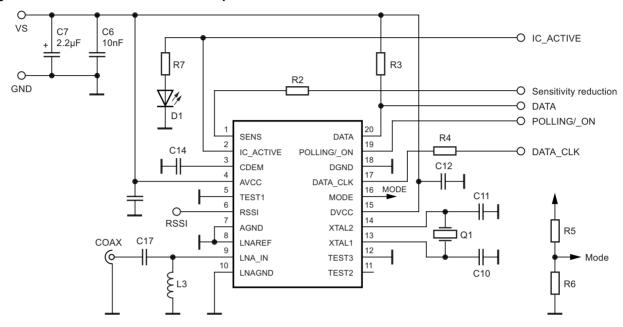

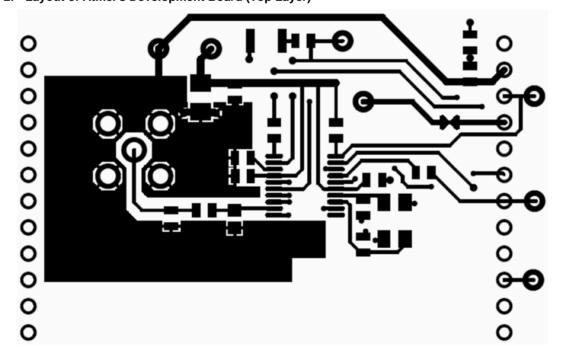

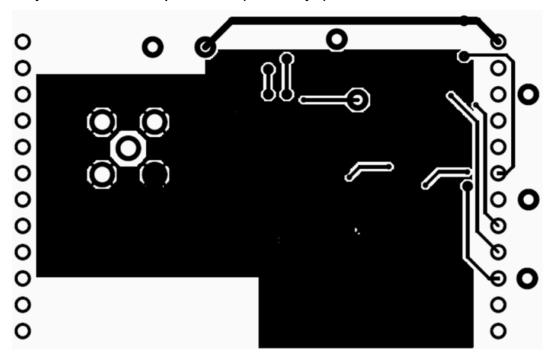

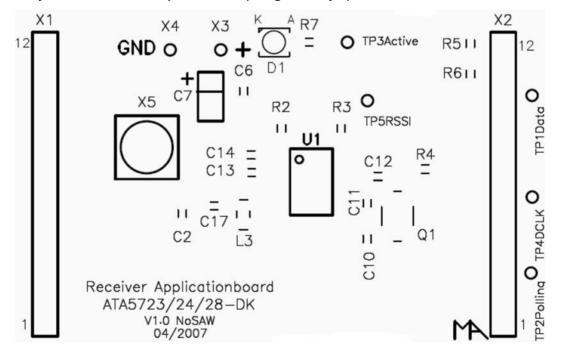

Atmel's receiver development boards can be ordered with the SAP number ATA5723-DK, ATA5724-DK and ATA5728-DK. The development boards contain an interface to the mother boards ATAB-RFMB or ATAB-STK-F. The connection with the mother boards allows the receivers to be configured with a personal computer via the serial data interface. Figure 2-1 shows the schematic of the development boards. Figure 2-2 to Figure 2-4 show the layout of the development board. The bill of material is listed in the Table 2-1 on page 10.

Figure 2-1. Schematic of Atmel's Development Board

Figure 2-2. Layout of Atmel's Development Board (Top Layer)

Figure 2-3. Layout of Atmel's Development Board (Bottom Layer)

Figure 2-4. Layout of Atmel's Development Board (Designator Layer)

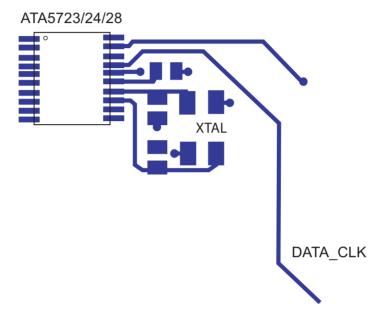

Layout hints for a general application using the receivers:

- 1. The blocking capacitors (for AVCC and DVCC) must be placed as near as possible to the IC.

- If the signal from the DATA\_CLK will be used and connected to a microprocessor, the trace for this connection

must be designed as short as possible and as far as possible from the crystal area. Figure 2-5 shows an ineffectual design for the DATA CLK trace.

- 3. If the trace between DATA\_CLK and the microprocessor is relative long, a resistor can be inserted in series into the trace. This is particularly useful if EMC and coupling effects are a design issue.

Figure 2-5. An Example of a Bad Wiring of the DATA\_CLCK Trace

Table 2-1. Bill of Material of the Development Boards

|                                                              |     |        |        | Comp   | onent List ATA5723/            | 24/28-DK V | 1.0               |                        |                            |

|--------------------------------------------------------------|-----|--------|--------|--------|--------------------------------|------------|-------------------|------------------------|----------------------------|

| Components                                                   | pcs | 315MHz | 433MHz | 868MHz | Value                          | Tolerance  | Material/Series   | Housing                | Manufacture<br>Distributor |

| U1                                                           | 1   | х      |        |        | ATA5723                        |            |                   | SS020                  | Atmel <sup>®</sup>         |

|                                                              |     |        | х      |        | ATA5724                        |            |                   | SS020                  | Atmel                      |

|                                                              |     |        |        | х      | ATA5728                        |            |                   | SS020                  | Atmel                      |

| R2                                                           | 1   | Х      | х      | Х      | 56k                            | 5%         | SMD               | 0603                   |                            |

| R3                                                           | 1   | Х      | х      | Х      | 8.2k                           | 5%         | SMD               | 0603                   |                            |

| R4                                                           | 1   | Х      | х      | Х      | 0                              |            | SMD               | 0603                   |                            |

| R5                                                           | 1   |        | х      | х      | 10k                            | 5%         | SMD               | 0603                   |                            |

| R6                                                           | 1   | Х      |        |        | 10k                            | 5%         | SMD               | 0603                   |                            |

| R7                                                           | 1   | х      | х      | х      | 1.8k                           | 5%         | SMD               | 0603                   |                            |

| C2                                                           |     |        |        |        | n.m.                           |            |                   |                        |                            |

| C6, C12, C13                                                 | 3   | х      | х      | х      | 10nF                           | 10%        | X7R               | 0603                   | Murata®                    |

| C7                                                           | 1   | х      | х      | х      | 2.2µ/35V                       | 20%        | Tantal            | Size 3528<br>mm/BfB    |                            |

| C10, C11                                                     | 2   | х      | х      | Х      | 18pF                           | 5%         | COG               | 0603                   | Murata                     |

| C14                                                          | 1   | х      | х      | Х      | 39n                            | 10%        | X7R               | 0603                   | Murata                     |

| C17                                                          | 1   | х      |        |        | 3pF                            | 5%         | COG               | 0603                   | Murata                     |

|                                                              |     |        | х      |        | 2.2pF                          | 5%         | COG               | 0603                   | Murata                     |

|                                                              |     |        |        | х      | 1.8pF                          | 5%         | COG               | 0603                   | Murata                     |

| D1                                                           | 1   | х      | х      | x      | х                              | TLMD3100   |                   | P-LCC-2<br>(sizeB)     | Vishay <sup>®</sup>        |

|                                                              | 1   | Х      |        |        | 39nH                           | 5%         | FSL               | LL1608                 | TOKO <sup>®</sup>          |

| L3                                                           |     |        | х      |        | 22nH                           | 5%         | FSL               | LL1608                 | TOKO                       |

|                                                              |     |        |        | х      | 5.6nH                          | 5%         | FSL               | LL1608                 | TOKO                       |

|                                                              | 1   | Х      |        |        | 14.71875MHz                    |            |                   | Metal lid              |                            |

| Q1                                                           |     |        | Х      |        | 13.528MHz                      |            |                   | 5mm × KDS              | KDS                        |

|                                                              |     |        |        | х      | 13.55234MHz                    |            |                   | 3.2mm                  |                            |

| X1, X2                                                       | 2   | х      | х      | x      | Row connector                  |            | 800-10-012-10-001 | 12 pins/<br>0.1" pitch | CAB                        |

| X5                                                           |     | Х      | Х      | х      | SMB connector                  |            | R114 426 000      |                        | Radiall®                   |

| TP1Data,<br>TP2Polling,<br>TP3Active,<br>TP4DCLK,<br>TP5RSSI | 5   | x      | x      | x      | Pin connector - white          |            | 240-333           | Single pin             | Farnell                    |

| Х3                                                           | 1   | х      | х      | х      | Pin connector - red            |            | 240-345           |                        |                            |

| X4                                                           | 1   | Х      | Х      | х      | Pin connector - black          |            | 240-333           |                        |                            |

| PCB                                                          | 1   |        |        |        | ATA5723/24/28-DK<br>V1.0 NoSAW |            | FR4/1.5 mm        |                        | Wagner                     |

## 3. Evaluation of Receivers using ATA5723/24/28-DK and RF Design Kit Software

One of the benefits of using the receiver ATA5723/24/28 is the reuse of the ATA5743/60 software.

For evaluation with the Atmel's RF Design Kit software up to V1.05, the designer can use the existing settings of ATA5743 (ATA5760), as follow:

- Choose receiver setting "T5743 (315MHz)" for configuration of ATA5723

- Choose receiver setting "T5743 (433MHz)" for configuration of ATA5724

- Choose receiver setting "T5760 (868MHz)" for configuration of ATA5728

With the RF Design Kit software V1.06 the optimum settings for the receiver are implemented. The suitable receiver settings are described by receiver type as well as the operating frequency under the Receiver pull down menu, as follow:

- The setting "ATA5723 (315MHz)"

- The setting "ATA5724 (433MHz)"

- The setting "ATA5728 (868MHz)"

For a more detailed description of the RF Design Kit software and ATAB-RFMB (ATAB-STK-F), please refer to the application notes "ATAK57xx and ATAK862xx hardware description" and "ATAK57xx, ATAK57xx-F, ATAK862xx and ATAK862xx-F software description". The documents also explain how to evaluate the RF system Link between Atmel's receivers and suitable transmitter products.

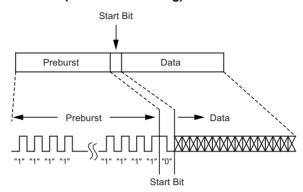

### 4. Consideration of the Transmission Protocol

Manchester coding is required for the optimal operation of the receivers. Therefore the explanation in this section assumes that the telegram of the system is Manchester encoded. For a general application, the recommended protocol will consist of preburst, start bit, and data. The preburst is the first part of the telegram with an identical number of bits, "111111..." as well as "00000...". The start bit is defined by changing the bit from "1" to "0" (or from "0" to "1"). Figure 4-1 illustrates this protocol.

Figure 4-1. The Recommended Protocol (Manchester Coding)

Preburst length is very important item in the definition of the protocol timing. This value depends on the defined sleep time, start-up time of the receiver, the number of the bit check and last but not least the start-up time of the microcontroller.

$$T_{Preburst} \ge T_{Sleep} + T_{Startup} + T_{Bit-check} + T_{Startup\_uC}$$

Equation 20

The following is an example for the definition of the preburst length. It is assumed that the system has the following requirements.

Receiving frequency: 433.92MHz

Data rate: 1kBps (Manchester)

Sleep time: 12.71ms

Number of the bit check: 3

Start-up time of the microcontroller: 1ms

The maximum time for the bit check ( $N_{Bit-Check} = 3$ ) will be estimated as  $3.5/f_{sig}$ . In case of 1kBps the  $T_{Bit-Ckeck} = 3.5$ ms.

The startup time for BR\_Range0 is 1.827ms (T<sub>Startup</sub>).

$$T_{Preburst} \ge 12.71 \text{ms} + 1.827 \text{ms} + 3.5 \text{ms} + 1 \text{ms} = 19.037 \text{ms}$$

T<sub>Preburst</sub> ≥ 19.037ms, which a means minimum 20 bits (Manchester) are only necessary for the preburst. For security the number of preburst bits can be defined as 25 bits.

### 5. Bit Check Limits

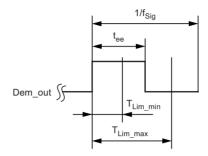

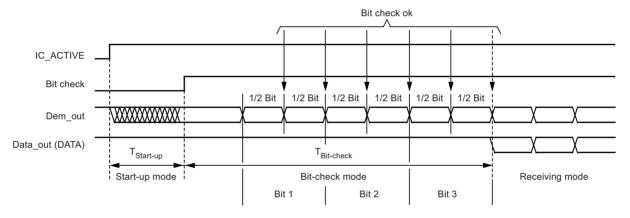

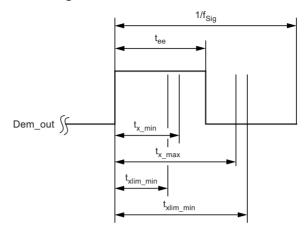

The basic of the bit check processing is the internally measurement of the timing between EDGE to EDGE (please see Figure 5-1) on the demodulator output.  $T_{\text{Lim\_min}}$  and  $T_{\text{Lim\_max}}$  create the time window for bit check processing. Both values can be set in the Limit Register of the receiver.

Figure 5-1. Valid Time Window for Bit Check

Figure 5-2 shows an example of a successful bit check with the NBit\_Check = 3. The number of bit check means here the number of Manchester encoded bit. If the bit check is successful the receiver leaves the bit check mode and the data will be transferred to the pin DATA (receiving mode).

Figure 5-2. Successful Bit Check Processing with Bit Check = 3

Note: ½ Bit here means ½ Manchester encoded Bit

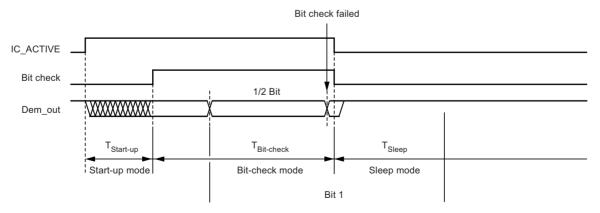

Figure 5-3. Failed Bit Check Processing

Figure 5-3 shows a failed bit check. As soon as the bit check failed, the receiver breaks the bit check processing and goes into the sleep mode.

The limits of the bit check must be defined very carefully because these values determine both the wake-up behavior and the sensitivity of the receiver. The limit values must be set such that the receiver will not be woken up by noise and the sensitivity will not be reduced. The calculation of the limit must consider the jitter effect of the signal, which occurs in case of a weak input signal. The best compromise between the sensitivity and the susceptibility to noise will be achieved with a bit check's valid time window between  $\pm 25\%$  to  $\pm 30\%$ .

The equations 21 and 22 show the correlation between the bit check's time limit and the setting values in the LIMIT register.

$T_{lim min} = Lim_{min} \times T_{xclk}$

Equation 21

$T_{lim\ max} = (Lim\_max-1) \times T_{xclk}$

Equation 22

Note:

Lim\_Min and Lim\_max are the values set in the LIMIT register.

T<sub>XCLK</sub> is the extended basic clock cycle for the different data ranges

- T<sub>XCLK</sub> for BR\_Range0 is 8xT<sub>CLK</sub>

- T<sub>XCLK</sub> for BR\_Range1 is 4xT<sub>CLK</sub>

- T<sub>XCLK</sub> for BR\_Range2 is 2xT<sub>CLK</sub>

- T<sub>XCLK</sub> for BR\_Range3 is 1xT<sub>CLK</sub>

-  $T_{CLK}$  is the basic clock cycle and derived from the crystal frequency. For ATA5723, this value will be defined as  $30/f_{XTO}$ , whereas for ATA5724/28 the value is  $28/f_{XTO}$ .

Equation 23

In addition to the bit check limits, there are 2 other important limit values in respect to the time violation of the Manchester coding, the Lim\_min2T and Lim\_max2T. The values will be internally calculated based on the values of Lim\_min and Lim\_max.

$Lim_min2T = (Lim_min + Lim_max) - (Lim_max-Lim_min) \times 0.5$

Lim max2T = (Lim min + Lim max) + (Lim max-Lim min)  $\times$  0.5 Equation 24

For the example calculation in this section  $T_{lim\_min}$  and  $T_{lim\_max}$  are defined with ±25% of the 0.5 ×  $T_{sig}$ . The values  $T_{lim\_min2T}$  and  $T_{lim\_max2T}$  must be calculated with ±12.5% of  $T_{sig}$ .

$$T_{lim\ min} = 0.75/(2 \times f_{sig}) \rightarrow Lim\_min = 0.75/(2 \times f_{sig} \times T_{XCLK})$$

$$T_{lim\ max} = 1.25/(2 \times f_{sig}) \rightarrow Lim_{max} = [1.25/(2 \times f_{sig} \times T_{XCLK})] + 1$$

$$Lim\_min2T = [3.5/(4 \times f_{sig} \times T_{XCLK})] + 0.5$$

$Lim_{max2T} = [4.5/(4 \times f_{sig} \times T_{XCLK})] + 1.5$

#### 5.1 Calculating the Limit Values Due to the Tolerance on the Transmitted Data Rate

For the calculation, the data rate including tolerance must be converted into periods. Assume the tolerance of the data rate is x% and the data rate's frequency is  $f_v$  (the period of the data rate  $(T_v)$  is  $1/f_v$ ).

The frequency range for the data rate is given by:

$$f_x \times \left(1 - \left[\frac{x}{100}\right]\right) \le f_x \le f_x \times \left(1 + \left[\frac{x}{100}\right]\right)$$

Equation 25

The period range of the data rate will be:

$$\frac{1}{f_x \times \left(1 - \left[\frac{x}{100}\right]\right)} \ge \frac{1}{f_x} \ge \frac{1}{f_x \times \left(1 + \left[\frac{x}{100}\right]\right)}$$

Equation 26

$$T_x \times \left(\frac{1}{1 - \left[\frac{x}{100}\right]}\right) \ge T_x \ge T_x \times \left(\frac{1}{1 + \left[\frac{x}{100}\right]}\right)$$

Equation 27

Figure 5-4 shows the setting of the time limit required for a successful bit check.

Figure 5-4. The Required Time Limit Ranges for a Successful Bit Check

Note:

Notes to Figure 5-4:

- $t_{x \ min}$  and  $t_{x \ max}$  are the possible jitter of the data rate to be received.

- $t_{\text{xlim min}}^-$  and  $\overline{t}_{\text{xlim max}}^-$  are the limit values that must be set for an optimal bit check, when the tolerance of the data rate is taken into account.

$$\begin{split} f_x &= \frac{T_x}{2} \rightarrow \ t_{x\_min} = \frac{T_x}{2} \times \left( \frac{1}{1 + \left[ \frac{x}{100} \right]} \right) \end{split} \qquad \text{Equation 28} \\ t_{x\_max} &= \frac{T_x}{2} \times \left( \frac{1}{1 - \left[ \frac{x}{100} \right]} \right) \end{split} \qquad \text{Equation 29}$$

The recommended 25% of the limit values:

$$t_{\text{xlim\_min}} = 0.75 \times \frac{T_{\text{x}}}{2} \times \left(\frac{1}{1 + \left[\frac{x}{100}\right]}\right)$$

Equation 30

$$t_{\text{xlim\_max}} = 1,25 \times \frac{T_{\text{x}}}{2} \times \left(\frac{1}{1 - \left[\frac{x}{100}\right]}\right)$$

Equation 31

The values of the limit\_2T will be calculated internally as follows (±12.5%):

$$t_{\text{xlim\_min }2T} = 0.875 \times T_{\text{x}} \times \left(\frac{1}{1 + \left[\frac{\text{x}}{100}\right]}\right) \qquad \text{Equation } 32$$

$$t_{\text{xlim\_max }2T} = 1.125 \times T_{\text{x}} \times \left(\frac{1}{1 - \left[\frac{\text{x}}{100}\right]}\right) \qquad \text{Equation } 33$$

### 5.2 Example

Data rate = 2.2kBit/s ( $f_{sig}$ ) with a tolerance of  $\pm 5\%$

$T_{xclk}$  = 8.278µs  $\approx$  8.3µs (for receiving frequency at 433.92MHz)

$$2200 \times \left(1 - \left[\frac{5}{100}\right]\right) \le f_x \le 2200 \times \left(1 + \left[\frac{5}{100}\right]\right) \Rightarrow 2090 \text{Hz} \le f_x \le 2310 \text{Hz}$$

$$T_{x} \times \left(\frac{1}{1 - \left\lceil \frac{x}{100} \right\rceil} \right) \ge T_{x} \ge T_{x} \times \left(\frac{1}{1 + \left\lceil \frac{x}{100} \right\rceil} \right) \Rightarrow 478.47 \mu s \ge T_{x} \ge 432.9 \mu s$$

The tolerance of the data rate's period is -4.8% and +5.3%.

$$t_{\text{xlim\_min}} = 0.75 \times \frac{T_x}{2} \times \left(\frac{1}{1 + \left[\frac{x}{100}\right]}\right) = 0.75 \times \frac{432.9}{2} = 162.34 \mu s$$

$$t_{\text{xlim\_max}} = 1.25 \times \frac{T_x}{2} \times \left(\frac{1}{1 - \left[\frac{x}{100}\right]}\right) = 1.25 \times \frac{478.47}{2} = 299.04 \mu s$$

$$t_{\text{xlim\_min }2T} = 0.875 \times T_x \times \left(\frac{1}{1 + \left[\frac{x}{100}\right]}\right) = 0.875 \times 432.9 = 378.79 \mu s$$

$$t_{\text{xlim}_{\text{max }2T}} = 1.125 \times T_{\text{x}} \times \left(\frac{1}{1 - \left\lceil \frac{\text{x}}{100} \right\rceil}\right) = 1.125 \times 478.47 = 538.28 \mu \text{s}$$

The possible setting Lim min = 17 and Lim max = 39 in the Limit register means:

$$T_{\text{Lim min}} = 17 \times 8.3 \mu s = 141.1 \mu s$$

$$T_{Lim\ max} = (39 - 1) \times 8.3 \mu s = 315.4 \mu s$$

The values are optimal for the bit check because:

$$T_{lim min} < t_{xlim min}$$

and  $T_{lim max} > t_{xlim max}$

The limit setting is also optimal for the perfect Manchester coding:

$$Lim_min2T = 45 T_{lim_min2T} = 373.5 \mu s < t_{xlim_min2T}$$

$$Lim\_max2T = 67 T_{lim max2T} = 556.1 \mu s > t_{xlim max2T}$$

### 6. DATA filter

The data filter circuitry of the analog signal processing is mostly integrated except for the external capacitor CDEM, which determines the lower cut-off frequency of the data filter ( $f_{cu\_DF}$ ) together with the internal resistor of  $30k\Omega$ . The capacitor's value must set according to the desired data ranges. The upper cut-off frequency ( $f_{u\_DF}$ ) is defined automatically by the setting of the BR\_Range. Equation 34 shows the calculation of the lower cut-off frequency.

$$f_{CU\_DF} = \frac{1}{2\pi \times 30 \text{ k}\Omega \times \text{CDEM}}$$

Equation 34

Table 6-1. The Recommended CDEM Value of the Related Data Filter's Cut-off Frequency

|           | CDEM  | Lower cut-off Frequency | Upper cut-off Frequency |

|-----------|-------|-------------------------|-------------------------|

| BR_Range0 | 39nF  | 0.136kHz                | 3.4kHz                  |

| BR_Range1 | 22nF  | 0.241kHz                | 6kHz                    |

| BR_Range2 | 12nF  | 0.442kHz                | 10kHz                   |

| BR_Range3 | 8.2nF | 0.647kHz                | 19kHz                   |

### 7. IC\_ACTIVE for LNA

The pin IC\_ACTIVE is designed to signal the status of the receiver, i.e., if the receiver is in sleep mode or active (receiving) mode. Therefore, this pin can be also used to control the biasing of an external preamplifier to boost the sensitivity of the receiver. The pin is specified for a current consumption of 1 mA. Therefore, is the pin is suitable only for biasing of the preamplifier and can not drive the preamplifier's supply current. The saturation voltage of the pin is specified as a typical value of 4.85V and minimum value of 4.6V.

### 8. The External Circuitry of Pin DATA

### 8.1 Determining the Pull-up Resistor Depends on the Load Capacitance

The load capacitance on the pin must be taken into account as this can influence the signal quality passed through this pin. Depending on the load capacitance on the pin and the data rate, the pull-up resistor on that pin must be properly determined. Table 8-1 shows the resistor ranges for different data rate ranges for two load capacitance values.

Table 8-1. The Recommended Pull-up Resistor (Datasheet Page 32, Table 14-1)

| •                      | BR_range | Applicable R <sub>pup</sub>    |

|------------------------|----------|--------------------------------|

|                        | В0       | 1.6k $\Omega$ to 47k $\Omega$  |

| C <sub>1</sub> ≤ 1nF   | B1       | 1.6k $\Omega$ to 22k $\Omega$  |

| OL 3 IIII              | B2       | 1.6k $\Omega$ to 12k $\Omega$  |

|                        | B3       | 1.6k $\Omega$ to 5.6k $\Omega$ |

|                        | В0       | 1.6k $\Omega$ to 470k $\Omega$ |

| C <sub>L</sub> ≤ 100pF | B1       | 1.6k $\Omega$ to 220k $\Omega$ |

| O <sub>L</sub> ≥ 100pr | B2       | 1.6kΩ to 120kΩ                 |

|                        | B3       | 1.6k $\Omega$ to 56k $\Omega$  |

### 8.2 Some Hints for Connecting the Pin Data Directly to another Control Module

The following conditions can be found in some automotive applications,

- The receiver module doesn't have its own microprocessor. The programming of the receiver as well as the received data processing will be performed by another control module.

- The only connection between the receiver module and the control module is the data interface on pin 20, which is connected directly to the power supply over a pull-up resistor.

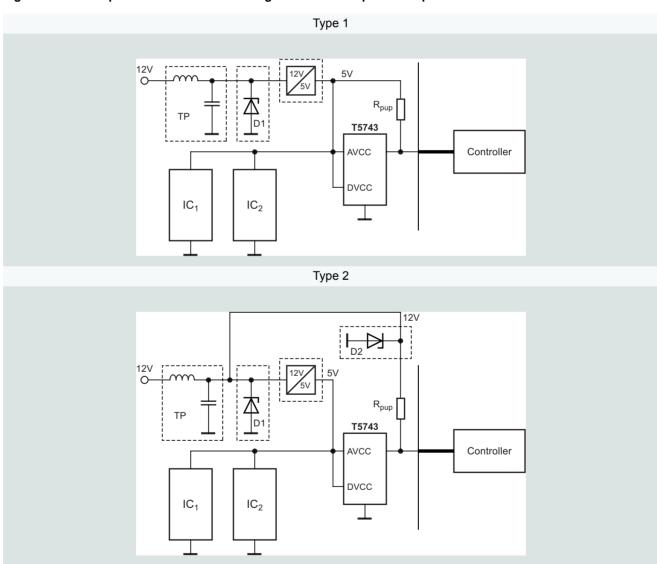

For this type of application, the receiver circuitry must be protected against both load dump and jump start.

#### 8.2.1 Principle Circuit for Protection against Load Dump and Jump Start

Figure 8-1 type 1 and type 2 give two possibilities for a protecting circuit. In the first circuit type 1, the protection will be performed by the LC low-pass filter, the protection diode (D1) as well as the voltage regulator. Depending on the needs, the inductor can be replaced by a resistor. A TVS (Transient Voltage Suppressor) diode is optimal for D1. In some cases a Zener diode can be used also.

Figure 8-1. Principle Circuit of a Protection against Load Dump and Jump Start

In the circuit type 2 the pull up resistor is connected directly to the 12V power supply instead of 5V regulated power supply. A protecting diode D2 must be placed between the power supply line and the pull-up resistor protecting the data out.

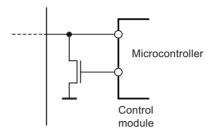

#### 8.2.2 Shifting of the Ground Potential

A "relatively" long connection between the receiver (pin data) and the control module can cause a fail of programming because of a different ground potential between the control module and the receiver module. This "shift" of the ground potential could distort the signal low level decision. If the receiver can not detect the low level set by the microprocessor, the circuit can not be programmed successfully. Generally the pin data can recognize a signal voltage  $0.35 \times V_S = 0.35 \times 5V$  d 1.7V as "LOW". This must be secured also in case of production variations. One possible solution would be to use a switch transistor in the control module, as illustrated in Figure 8-2.

Figure 8-2. Principle Application Circuit with a Switch Transistor Controlling the Serial Data Interface of the Receiver

# 9. Revision History

Please note that the following page numbers referred to in this section refer to the specific revision mentioned, not to this document.

| Revision No.     | History                                                                                                                          |

|------------------|----------------------------------------------------------------------------------------------------------------------------------|

| 9118C-AUTO-05/15 | Put document in the latest template                                                                                              |

|                  | Section 2 "Calculating the Required Crystal Frequency" on page 2 updated                                                         |

| 9118B-AUTO-09/08 | <ul> <li>Section 5 "Evaluation of Receivers using ATA5723/24/28-DK and RF Design Kit<br/>Software" on page 12 updated</li> </ul> |

T: (+1)(408) 441.0311 **Atmel Corporation** 1600 Technology Drive, San Jose, CA 95110 USA

F: (+1)(408) 436.4200

www.atmel.com

© 2015 Atmel Corporation. / Rev.: 9118C-AUTO-05/15

Atmel®, Atmel logo and combinations thereof, Enabling Unlimited Possibilities®, and others are registered trademarks or trademarks of Atmel Corporation in U.S. and other countries. Other terms and product names may be trademarks of others.

DISCLAIMER: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL WEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS AND PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and products descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

SAFETY-CRITICAL, MILITARY, AND AUTOMOTIVE APPLICATIONS DISCLAIMER: Atmel products are not designed for and will not be used in connection with any applications where the failure of such products would reasonably be expected to result in significant personal injury or death ("Safety-Critical Applications") without an Atmel officer's specific written consent. Safety-Critical Applications include, without limitation, life support devices and systems, equipment or systems for the operation of nuclear facilities and weapons systems. Atmel products are not designed nor intended for use in military or aerospace applications or environments unless specifically designated by Atmel as military-grade. Atmel products are not designed nor intended for use in automotive applications unless specifically designated by Atmel as automotive-grade.