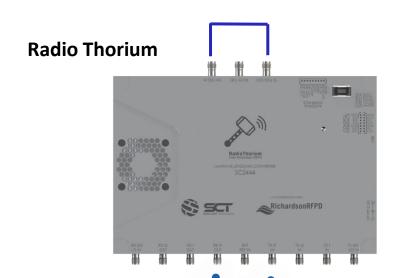

# **Radio Thorium Overview**

October 20<sup>th</sup>, 2022

## **Overview**

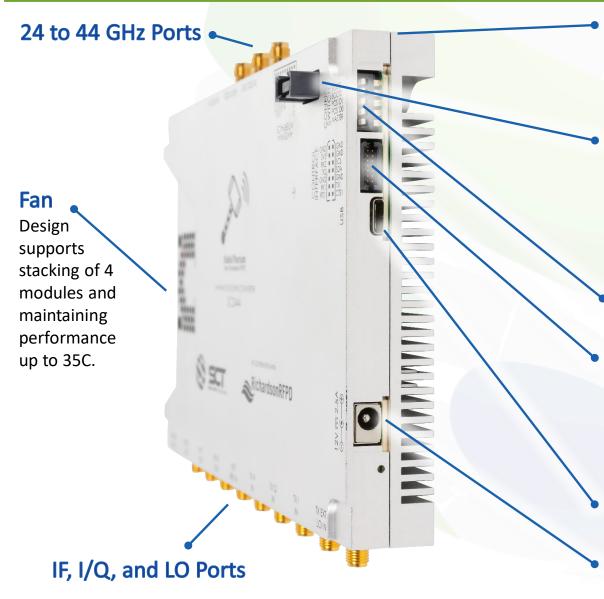

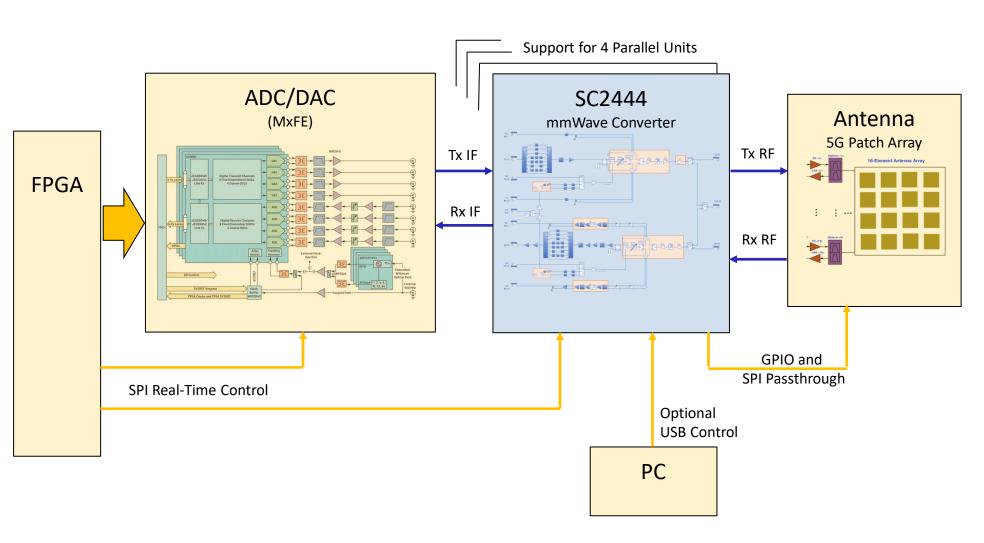

SCT created the SC2444 in partnership with RichardsonRFPD and Analog Devices. The SC2444 mmWave Converter is a stand-alone solution for use in the 24 to 44 GHz range. It is the first in a family of RadioThorium Branded Modules.

The module is designed to interface directly with an external baseband platform, such as Analog Device's MxFE (Mixed-Signal Front-End) or similar Software Defined Radios.

The modules are designed such that they can be cascaded to create complex 4x4 MIMO radio applications.

## **Features**

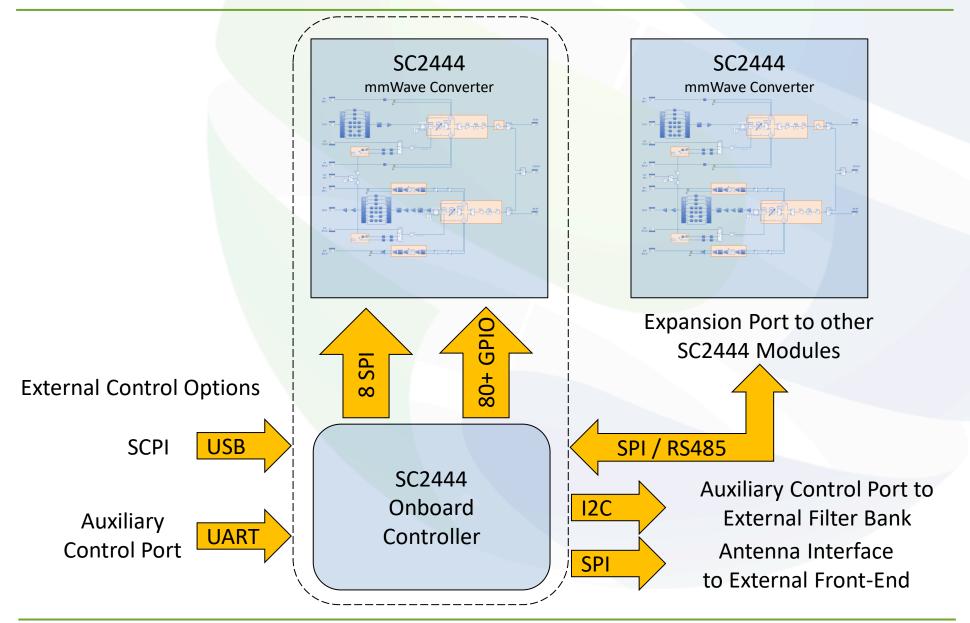

Control of the card is provided via either SPI or USB interfaces. The control interfaces can be cascaded (in series) to support a single, external controller. An API Control Interface Specification is provided with detailed command and timing information. Two control modes are available. The first is a console API based on SCPI/488.2. The second is a 32-bit binary structure, for automated control and timing critical applications.

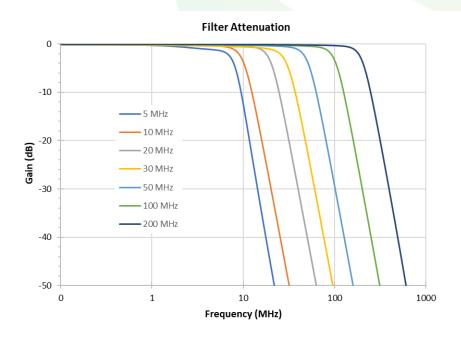

On the low frequency side, both up and down conversion paths support I/Q and IF interfaces. On-board I/Q buffers allow direct connection to external, single-ended ADC/DACs operating at up to 6 GHz. Programmable low pass filters (LPFs) in the buffers help reduce out of band spurious signals.

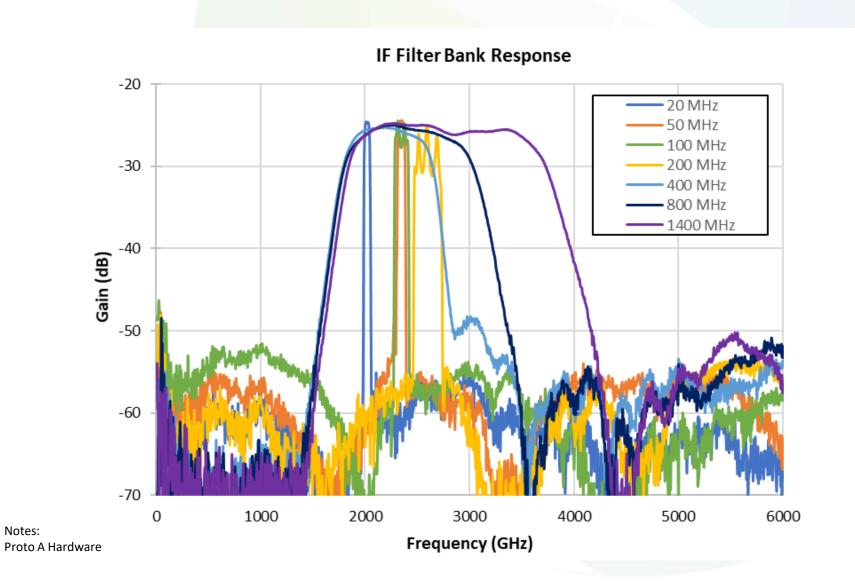

The IF ports are designed for the 2 to 6 GHz range. Onboard user selectable filter banks provide 20, 50, 100, 200, 400, 800, 1400 MHz bandwidths along with a bypass path option.

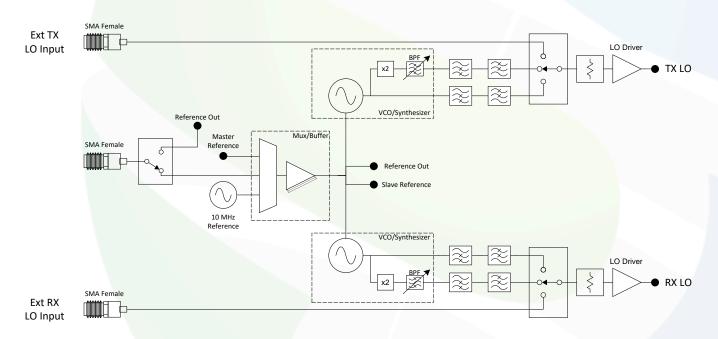

The SC2444 can used for either Time Division Duplex (TDD) or Frequency Division Duplex (FDD) systems. The UC and DC paths have separate, high-performance, local oscillators (LOs). Inputs on each path are also available for injection of external LO sources.

Both onboard and external frequency references are supported. The reference source is shared with both the UC and DC paths to provide phase coherence.

## **Key Features**

### **Antenna Interface**

Spare interface with SPI and GPIO pins to provide control for external devices such as antenna arrays or other frontends.

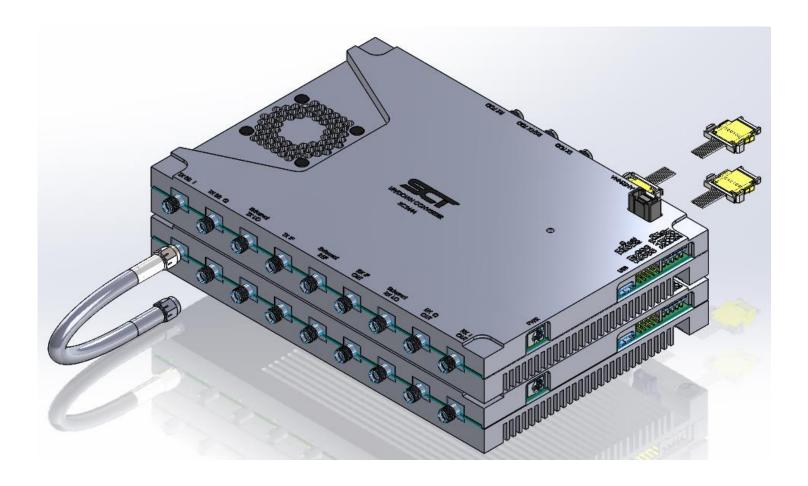

## **Expansion Port**

The port routes SPI, UART, and reference clock, and other control lines to other cascaded units that are mechanically stacked on top of each other. Up to 4 units can be controlled simultaneously via this port.

## **Config Port**

Device Addressing and Boot Mode Settings.

## **Auxiliary Control Interface**

Dual UARTS for use with external devices that don't support USB. An I2C Port is also available to power and control the optional external I/Q Filter Bank.

## **USB Control Interface**

USB 2 Type-C High Speed Device

## **Power Input**

Wall cube 12Vdc input.

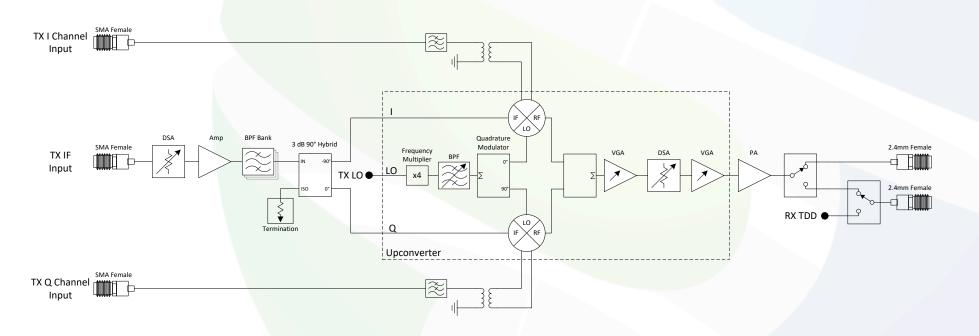

# **Upconverter Chain Block Diagram**

### **ADMV1013 Wideband, Microwave Upconverter**

- Wideband RF input frequency range: 24 GHz to 44 GHz

- 2 upconversion modes

- Direct conversion from baseband I/Q to RF

- Single-sideband upconversion from real IF

- LO input frequency range: 5.4 GHz to 10.25 GHz

- LO quadrupler for up to 41 GHz

- Sideband suppression and carrier feedthrough optimization

### **ADPA7002 Power Amplifier**

- Output P1dB: 28 dBm (typical at 34 GHz to 44 GHz)

- PSAT: 29.5 dBm (typical at 24 GHz to 34 GHz)

- Gain: 15 dB (typical at 34 GHz to 44 GHz)

- •IP3: 38 dBm (typical)

- Integrated power detector

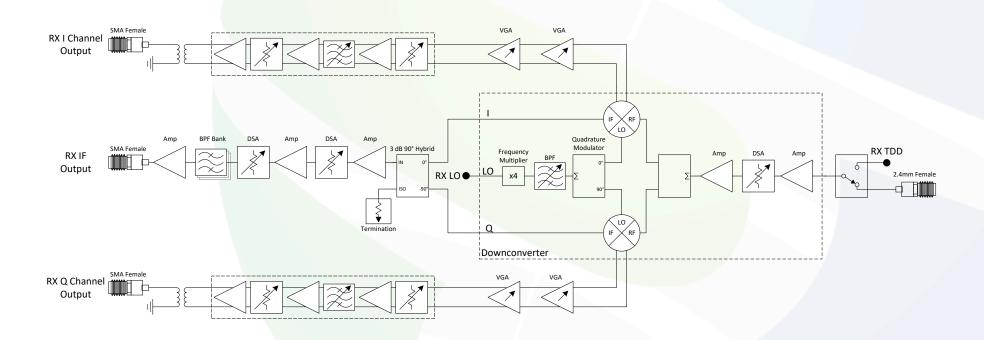

# **Downconverter Chain Block Diagram**

## ADMV1014 Wideband, Microwave Downconverter

- Wideband RF input frequency range: 24 GHz to 44 GHz

- Image rejecting downconversion to complex IF

- LO input frequency range: 5.4 GHz to 10.25 GHz

- LO quadrupler for up to 41 GHz LO

- Adjustable output common-mode voltage level

- Image rejection optimization

- Square law power detector for setting mixer input power

- Variable attenuator for Downconverter power control

### **ADRF5024 SPDT Reflective Switch**

- Ultrawideband frequency range: 100 MHz to 44 GHz

- Reflective design

- Low insertion loss with impedance match

- 1.4 dB typical to 40 GHz

- High input linearity

- P1dB: 27.5 dBm typical

- IP3: 50 dBm typical

# **On-Board Oscillators Block Diagram**

### **ADF4372 Wideband Synthesizer with VCO**

- RF output frequency range: 62.5 MHz to 16,000 MHz

- Fractional-N synthesizer and integer-N synthesizer

- High resolution 39-bit fractional modulus

- Typical spurious fPFD: -90 dBc

- Integrated rms jitter: 38 fs (1 kHz to 100 MHz)

- Normalized phase noise floor: -234 dBc/Hz

- fPFD operation to 250 MHz

- Reference input frequency operation to 600 MHz

- Programmable divide by 1, 2, 4, 8, 16, 32, or 64 output

## **Control Interfaces**

# **Controlling the SC2444**

Two distinct application protocols are incorporated into the SC2444.

- Console Protocol

- Available via USB and UART (TTL-levels) ports

- Targeted at command console or automated test environments

- Similar to SCPI / IEEE488.2

- Supports high level (ie. Set Synth Frequency) and low level (ie. Set Synth N Register) functions

- ASCII-based commands follow SCPI/IEEE488.2 structure

- Query command are terminated with a '?' character

- Example

- High level command to set the Tx LO frequency to 10.25 GHz using current configuration parameters (ie ext ref freq, comparison frequency, etc)

format SYN:OUT <channel ID> <direction> <output frequency>

### SYN:OUT TX 10250000

Low level command to set the synthesizer registers directly

format SYN:RFSET <channel ID> <direction> <INT> <FRAC1> <FRAC2> <MOD2> <RF Divider>

SYN:RFSET 0 TX 260 26039637 512 1536 2

# **Controlling the SC2444**

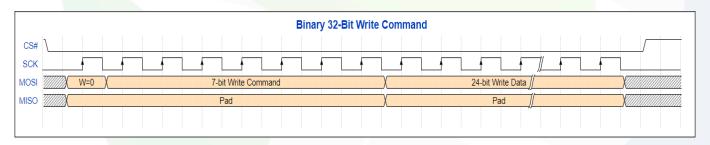

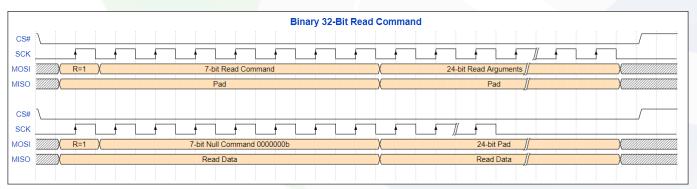

## 2. Binary Protocol

- Available via SPI port

- Targeted at FPGA, or similar, controllers

- Low level functions via 32-bit register-based interface

- Supports both write and read operations

## **Demo Setup Script**

```

// Setup the system as a Master with 1 Channel

SYS: ROLE Ø MASTER

SYS:NCHAN 0 1

// Configure the System Reference to 10 MHz

SYS:REF 0 10000

LOCLK: REF Ø INT OFF

// Configure the Synthesizer PFD to 20 MHz

SYN: PFDSET 0 TX 1 1 0

SYN: PFDSET 0 RX 1 1 0

// Configure the LO Frequency

LOCLK: FREO TX 24650000

LOCLK: FREQ RX 24650000

// Configure the Converter Mode

CV:MODE 0 TX IF

CV:MODE 0 RX IF

// Configure the IF Filters

IFPATH: FLT 0 TX 50

IFPATH: FLT 0 RX 50

// Configure the Converter Gain

// Assumes: TX input power <= -40 dBm

CV:VGAIN 0 TX 1.8

CV:VGAIN 0 RX 0.0

// Configure the IF Attenuation

// Assumes: TX input power <= -40 dBm

IFPATH: ATTN 0 TX 0

IFPATH: ATTN 0 RX 22 22

// Configure the RF Path

RFPATH: PATH Ø FDD

```

#### Reference:

- Configure the reference signal to use internal 10 MHz

- Configure the Synthesizer PFD for 20 MHz

#### **Upconverter:**

- IF input of 2.345 GHz with a bandwidth of 50 MHz

- Configure IF input filter to 50 MHz

- RF output of 26.985 GHz (upper sideband)

- Configure the internal synthesizer for an LO of 24.650 GHz

- Enables the RF8 output of the synthesizer

- Switches the RF8 output to the Converter LO input

- Configures the Synthesizer output to 6.160 GHz

- The converter multiplies the LO by 4x

- (Frequency / PFD) = Integer Value for best performance

- o Configures the Converter to use the LO Filter 5.4 GHz 7 GHz

#### Downconverter:

- RF input of 26.985 GHz (upper sideband)

- IF output of 2.345 GHz with a bandwidth of 50 MHz

- Configure IF output filter to 50 MHz

- Configure the internal synthesizer for an LO of 24.650 GHz

- Enables the RF8 output of the synthesizer

- Switches the RF8 output to the Converter LO input

- Configures the Synthesizer output to 6.160 GHz

- The converter multiplies the LO by 4x

- (Frequency / PFD) = Integer Value for best performance

- Configures the Converter to use the LO Filter 5.4 GHz 7 GHz

#### Output:

· Select FDD mode.

# **Typical Application**

# **Multi-Module Support**

Architecture supports operation of 4 modules in parallel.

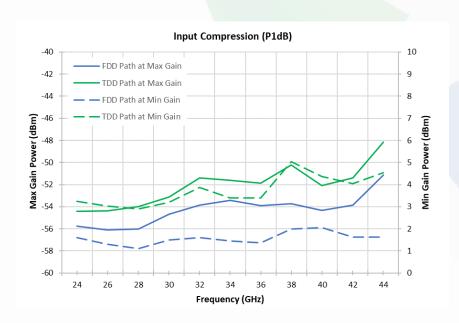

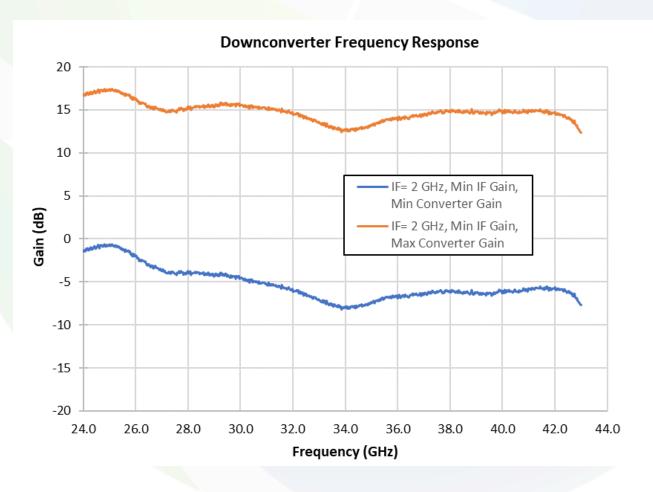

## **Down-Conversion Path (IF Output)**

The Down-Conversion (UC) path in FDD mode has an input P1dB of 0 dBm (min gain) and max gain of 75 dB at 40 GHz.

In TDD mode, the input P1dB at 40 GHz is 0 dBm and has a gain of 72 dB.

# **Up-Conversion Path (IF Input)**

The Up-Conversion (UC) path in FDD mode has a gain of 33 dB and output compression point (P1dB) of 18 dBm at 40 GHz.

In TDD mode, the P1dB at 40 GHz is 16 dBm at a gain of 32 dB.

The Power Amplifier (PA) is biased using an onboard controller, giving the user some control over its operating conditions.

# **Optional I/Q Filter Bank**

The SC4710 in an external Switched Filter Bank that can be used to clean In-Phase and Quadrature signals prior to injection to the converter. It can be controlled directly by the SC2444 via I2C on its Secondary Control Interface.

## **Demo**

### **External Monitor**

Vector Signal Transceiver (SDR)

And PXI-based Controller

Baseband Filter Bank (Optional)

# **Downconverter Response**

| Settings       |              |  |

|----------------|--------------|--|

| RF Frequency   | 24 to 44 GHz |  |

| LO Power       | -3.0 dBm     |  |

| RF Input Power | -30 dBm      |  |

| RF Gain        | Min/Max      |  |

| IF Frequency   | 2 GHz        |  |

| IF Gain        | 0 dB         |  |

Notes:

Rev 1 Hardware (S/N 8D619006)

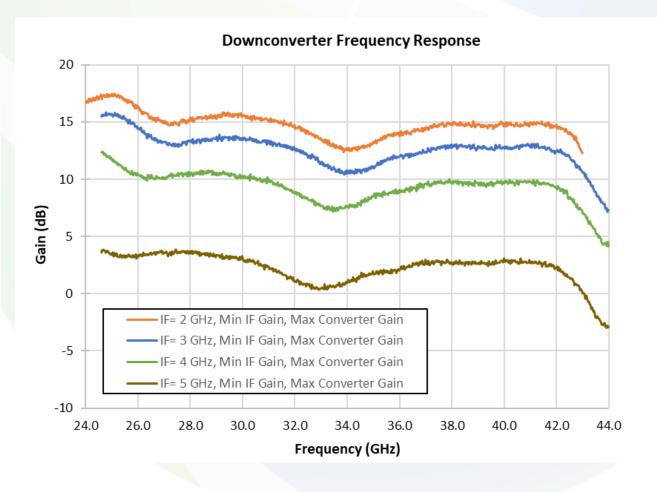

# **Downconverter Response**

| Settings       |              |

|----------------|--------------|

| RF Frequency   | 24 to 44 GHz |

| LO Power       | -3.0 dBm     |

| RF Input Power | -30 dBm      |

| RF Gain        | Max          |

| IQ Frequency   | 2,3,4,5 GHz  |

| IQ Gain        | 0 dB         |

Notes:

Rev 1 Hardware (S/N 8D619006)

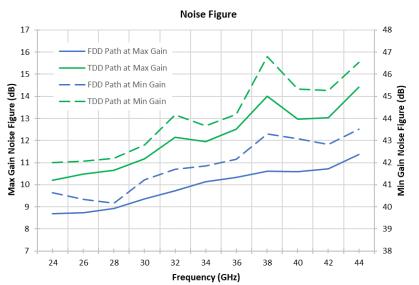

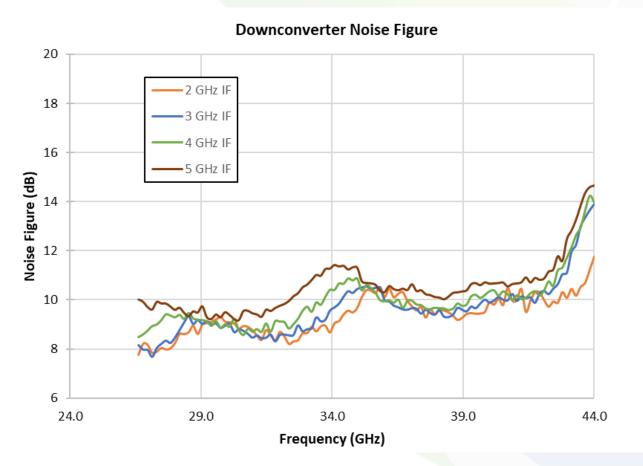

# **Downconverter Noise Figure**

| Settings       |              |

|----------------|--------------|

| RF Frequency   | 24 to 44 GHz |

| LO Power       | -3.0 dBm     |

| RF Input Power | -30 dBm      |

| RF Gain        | Max          |

| IF Frequency   | 2,3,4,5 GHz  |

Notes: Rev 1 Hardware (S/N 8D619006)

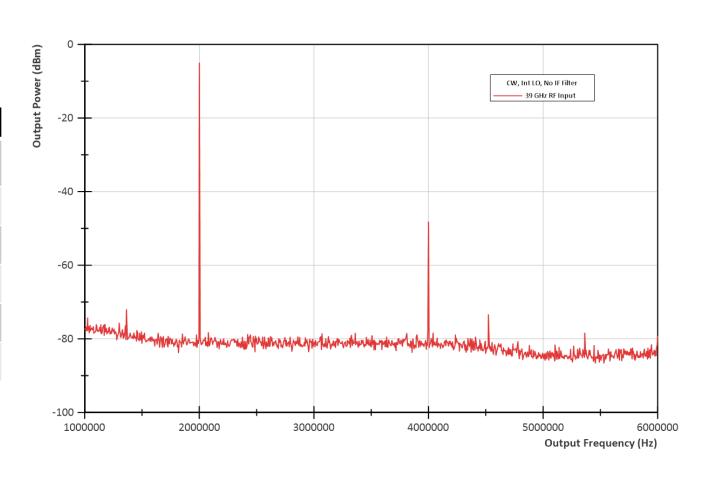

# **Downconverter IF Output Spectrum**

| Settings       |          |  |

|----------------|----------|--|

| RF Frequency   | 39 GHz   |  |

| LO Power       | -3.0 dBm |  |

| RF Input Power | tbd      |  |

| Gain           | Max      |  |

| IF Frequency   | 2.35 GHz |  |

| IF Gain        | 0 dB     |  |

Notes:

Rev 1.1 Hardware (S/N 8D619006)

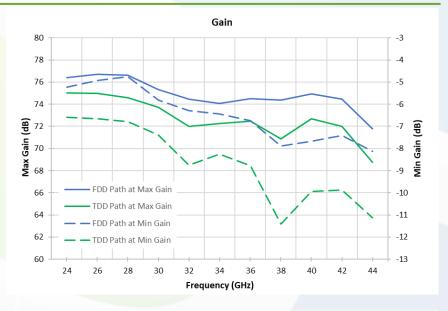

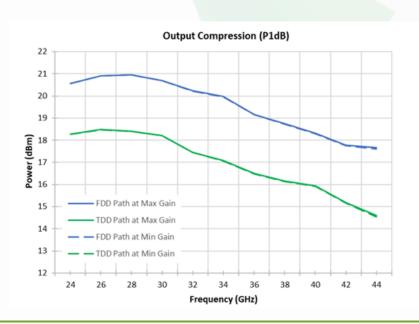

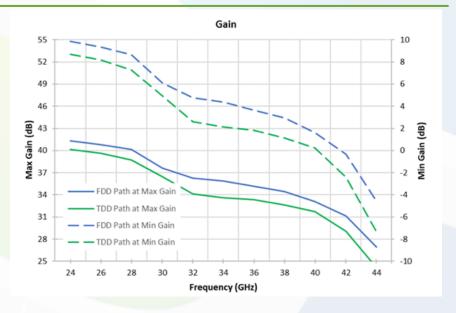

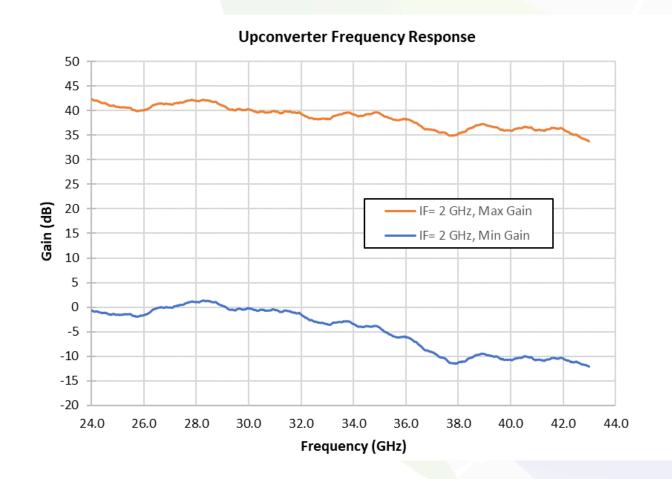

# **Upconverter Response**

| Settings       |              |  |

|----------------|--------------|--|

| RF Frequency   | 24 to 44 GHz |  |

| LO Power       | -3.0 dBm     |  |

| IF Input Power | -30 dBm      |  |

| Gain           | Min/Max      |  |

| IF Frequency   | 2 GHz        |  |

Notes: Rev 1 Hardware (S/N 8D619006)

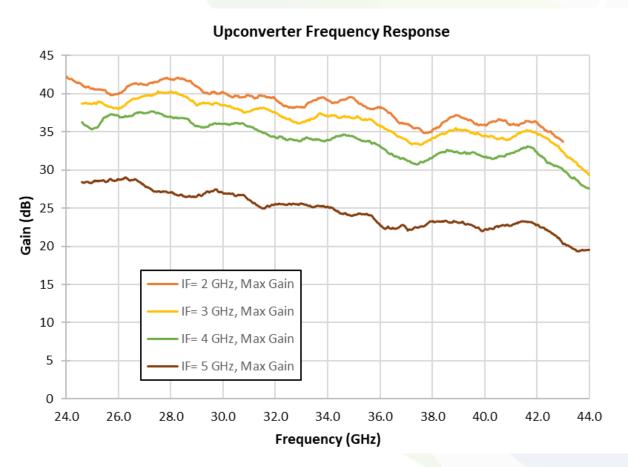

# **Upconverter Response**

| Settings       |                |  |

|----------------|----------------|--|

| RF Frequency   | 24 to 44 GHz   |  |

| LO Power       | -3.0 dBm       |  |

| IF Input Power | -30 dBm        |  |

| Gain           | Max            |  |

| IF Frequency   | 2, 3, 4, 5 GHz |  |

Notes: Rev 1 Hardware (S/N 8D619006)

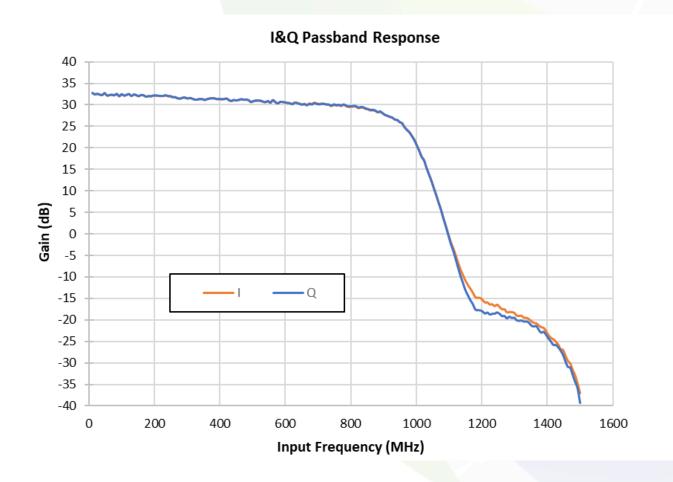

# **Upconverter IQ Passband Response**

| Settings       |          |  |

|----------------|----------|--|

| RF Frequency   | 24 GHz   |  |

| LO Power       | -3.0 dBm |  |

| IQ Input Power | -30 dBm  |  |

| Gain           | Max      |  |

| IQ Frequency   | Variable |  |

Notes:

Rev 1 Hardware (S/N 8D619006)

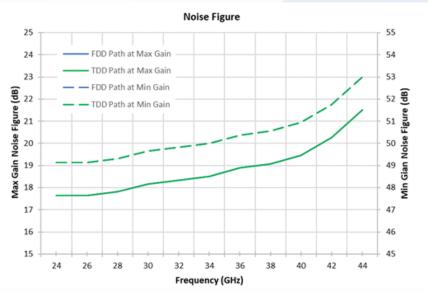

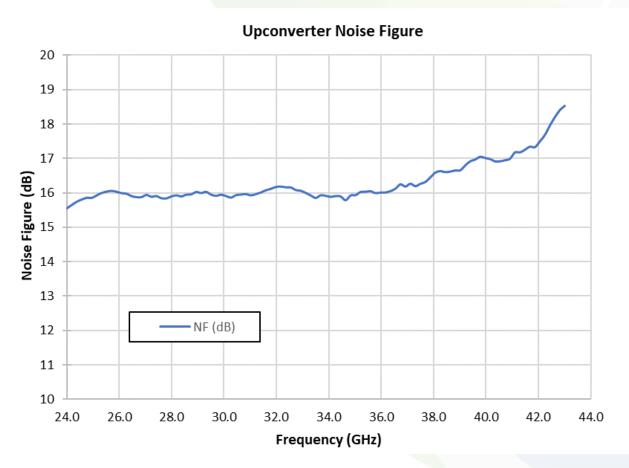

# **Upconverter Noise Figure**

| Settings       |              |  |

|----------------|--------------|--|

| RF Frequency   | 24 to 44 GHz |  |

| LO Power       | -3.0 dBm     |  |

| IF Input Power | -30 dBm      |  |

| Gain           | Max          |  |

| IF Frequency   | 2 GHz        |  |

Notes: Rev 1 Hardware (S/N 8D619006)

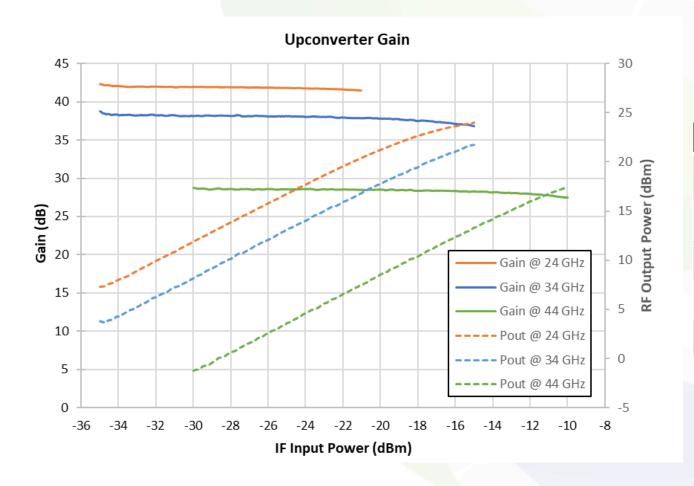

# **Upconverter Gain**

| Settings       |                |  |

|----------------|----------------|--|

| RF Frequency   | 24, 34, 44 GHz |  |

| LO Power       | -5 dBm         |  |

| IF Input Power | variable       |  |

| Gain           | Max            |  |

| IF Frequency   | 2 GHz          |  |

Notes: Rev 1 Hardware (S/N 8D619006)

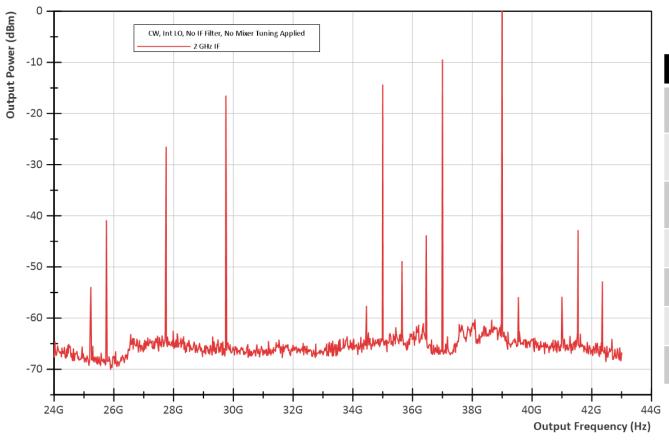

# **Upconverter Harmonic and Spurious Output**

| Settings       |          |  |

|----------------|----------|--|

| Output Freq    | 39 GHz   |  |

| Filtering      | None     |  |

| Mixer Tuning   | None     |  |

| LO Power       | -5 dBm   |  |

| IF Input Power | variable |  |

| Gain           | Max      |  |

| IF Frequency   | 2 GHz    |  |

Notes:

Rev 1 Hardware (S/N 8D619006)

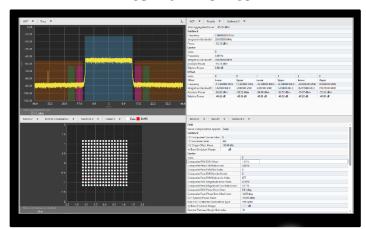

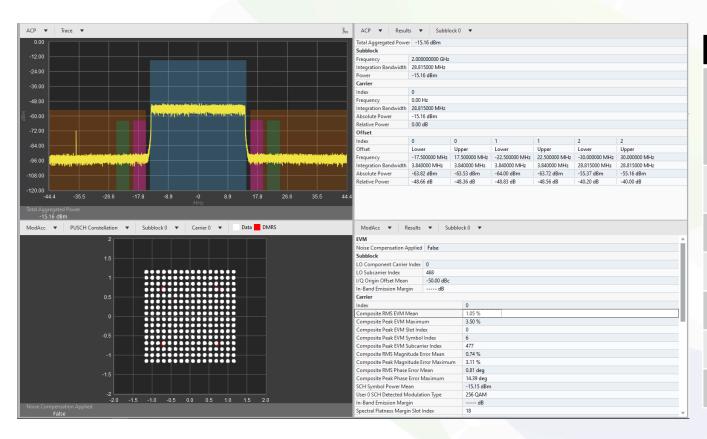

# **Example EVM Measurement**

| Settings                               |  |  |

|----------------------------------------|--|--|

| 5G<br>BW=30MHz<br>SCS=30kHz<br>256 QAM |  |  |

| 24 GHz                                 |  |  |

| 0 dBm                                  |  |  |

| -20 dBm                                |  |  |

| Max                                    |  |  |

| Max                                    |  |  |

| 2 GHz                                  |  |  |

|                                        |  |  |

Notes:

Rev 1 Hardware (S/N 8D619006)

Test Signal NR\_FR1\_UL\_FDD\_SISO\_BW-30MHz\_CC-1\_SCS-30kHz\_Mod-256QAM-OFDM

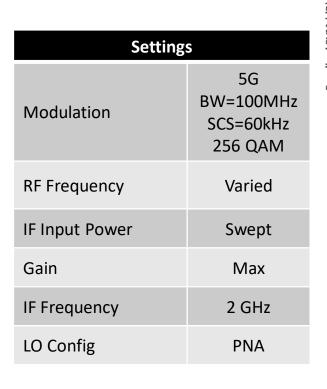

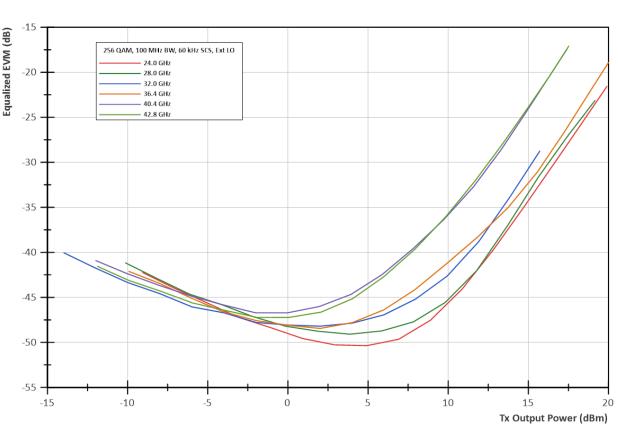

# **Upconverter Composite EVM vs Frequency**

#### Notes:

Rev 1.1 Hardware (S/N 8D619010)

Characterized with Keysight PNA-X using Equalized Mode

Test Signal NR\_FR1\_UL\_FDD\_SISO\_BW-100MHz\_CC-1\_SCS-60kHz\_Mod-256QAM-OFDM

### **EVM**

- Equalized EVM of the DUT (non-linear contribution)

- Un-equalized EVM of the DUT (Includes non-linear and linear distortion due to frequency dispersion)

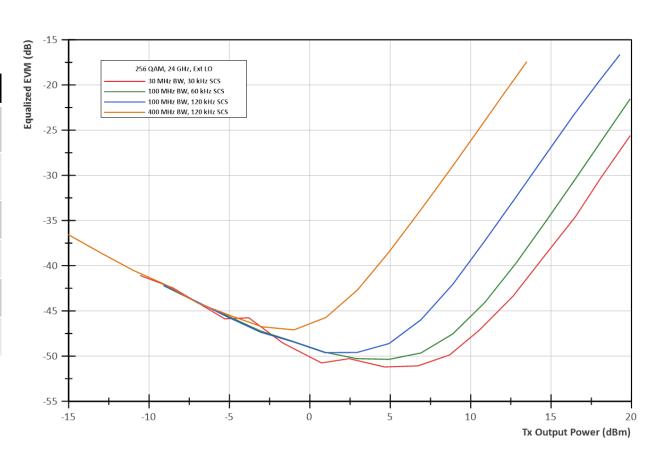

# **Upconverter Composite EVM vs BW**

| Settings       |        |

|----------------|--------|

| Modulation     | Varied |

| RF Frequency   | 24 GHz |

| IF Input Power | Swept  |

| Gain           | Max    |

| IF Frequency   | 2 GHz  |

| LO Config      | PNA    |

#### Notes:

Rev 1.1 Hardware (S/N 8D619010)

Characterized with Keysight PNA-X using Equalized Mode

$Test\ Signal\ NR\_FR1\_UL\_FDD\_SISO\_BW-100MHz\_CC-1\_SCS-60kHz\_Mod-256QAM-OFDM$

#### EVM

- Equalized EVM of the DUT (non-linear contribution)

- Un-equalized EVM of the DUT (Includes non-linear and linear distortion due to frequency dispersion)

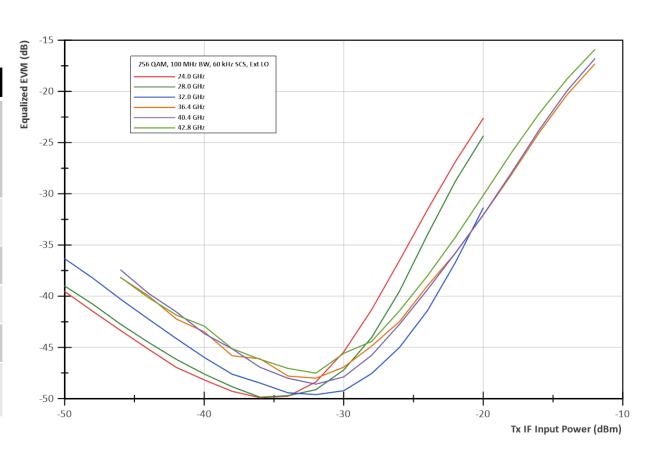

# **Loopback Composite EVM**

| Settings       |                                         |

|----------------|-----------------------------------------|

| Modulation     | 5G<br>BW=100MHz<br>SCS=60kHz<br>256 QAM |

| RF Frequency   | Varied                                  |

| IF Input Power | Swept                                   |

| Gain           | Max                                     |

| IF Frequency   | 2 GHz                                   |

| LO Config      | Independent<br>Internal                 |

#### Notes:

Rev 1.1 Hardware (S/N 8D619010)

Characterized with Keysight PNA-X using Equalized Mode

$Test\ Signal\ NR\_FR1\_UL\_FDD\_SISO\_BW-100MHz\_CC-1\_SCS-60kHz\_Mod-256QAM-OFDM$

### EVM

- Equalized EVM of the DUT (non-linear contribution)

- Un-equalized EVM of the DUT (Includes non-linear and linear distortion due to frequency dispersion)

Notes:

# **IF Filter Bank Responses**