# Dual, low-offset, low noise operational amplifier

**OP227**

#### 1.0 SCOPE

This specification documents the detail requirements for space qualified product manufactured on Analog Devices, Inc.'s QML certified line per MIL-PRF-38535 Level V except as modified herein. The manufacturing flow described in the STANDARD SPACE LEVEL PRODUCTS PROGRAM brochure is to be considered a part of this specification. <a href="http://www.analog.com/aerospace">http://www.analog.com/aerospace</a>

This data sheet specifically details the space grade version of this product. A more detailed operational description and a complete datasheet for commercial product grades can be found at <a href="https://www.analog.com/OP227">www.analog.com/OP227</a>

**2.0 Part Number**. The complete part number(s) of this specification follow:

| <u>Part Number</u> | <u>Description</u>                                                  |

|--------------------|---------------------------------------------------------------------|

| OP227-903Y         | Dual, low-offset, low noise operational amplifier                   |

| OP227R903Y         | Radiation Tested, Dual, low-offset, low noise operational amplifier |

| OP227-903M         | Dual, low-offset, low noise operational amplifier                   |

| OP227R903M         | Radiation Tested, Dual, low-offset, low noise operational amplifier |

#### 2.1 Case Outline.

| <u>Letter</u> | <u>Descriptive designator</u> | Case Outline (Lead Finish per MIL-PRF-38535)  |

|---------------|-------------------------------|-----------------------------------------------|

| Y             | GDIP1-T14                     | 14-Lead ceramic dual-in-line package (CERDIP) |

| M             | GDFP1-F14                     | 14-Lead ceramic flat pack (CERPAK)            |

### NOTES:

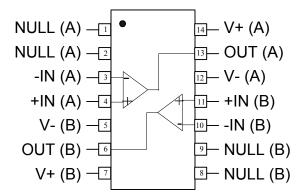

- 1. Device may be operated even if insertion is reversed; this is due to inherent symmetry of pin locations of amplifiers A and B

- 2. V-(A) and V-(B) are internally connected via substrate resistance.

Figure 1 - <u>Terminal connections</u>.

their respective companies.

## **OP227**

## 3.0 Absolute Maximum Ratings. 1/

| Supply voltage (V)                                    | ±22 V dc CC    |

|-------------------------------------------------------|----------------|

| Input voltage range (V)                               | ±22 V dc IN    |

| Output short circuit duration                         | Indefinite     |

| Differential input current <u>2/</u>                  | ±25 mA         |

| Differential input voltage range                      | ±0.7 V dc      |

| Lead temperature (soldering, 60 seconds)              | +300°C         |

| Storage temperature range                             | 65°C to +150°C |

| Maximum power dissipation (P <sub>D</sub> ) <u>3/</u> |                |

#### NOTES:

- 1/ Unless otherwise specified, all voltages are referenced to ground.

- 2/ The inputs are protected by back-to-back diodes. Current limiting resistors are not used in order to achieve low noise. If differential input voltage exceeds ±0.7 V, the input current should be limited to 25 mA.

- 3/ For T greater than 106°C, derate linearly at 11.3 mW/°C.

#### 3.1 Thermal Characteristics:

Thermal Resistance, Y (cerdip) Package

Junction-to-Case  $(\Theta_{JC}) = 29^{\circ}\text{C/W}$  Max

Junction-to-Ambient  $(\Theta_{JA}) = 91^{\circ}\text{C/W}$  Max

Thermal Resistance, M (cerpak) Package

Junction-to-Case  $(\Theta_{JC}) = 90^{\circ}\text{C/W}$  Max

Junction-to-Ambient  $(\Theta_{JA}) = 150^{\circ}\text{C/W}$  Max

#### 4.0 **Electrical Table**:

|                                        |                   | Table I                                                                 |                 |              |              |            |

|----------------------------------------|-------------------|-------------------------------------------------------------------------|-----------------|--------------|--------------|------------|

| Parameter<br>See notes at end of table | Symbol            | Conditions Note 1                                                       | Sub-<br>group   | Limit<br>Min | Limit<br>Max | Units      |

| Input offset voltage                   | $V_{IO}$          |                                                                         | 1 2, 3          |              | 80<br>180    | μV         |

| Average input offset drift 2/4/        | TCV <sub>IO</sub> | M, D, L, R                                                              | 1, 2, 3         |              | 160<br>1.0   | μV/°C      |

| Input offset current                   | I <sub>IO</sub>   |                                                                         | 1 2,3           |              | ±35<br>±50   |            |

| CINCIA SERSONALIZADOS SENSOLARIZADAS   | 10                | M, D, L, R                                                              | 1 1             |              | ±120<br>±40  | nA         |

| Input bias current                     | $I_{I\!B}$        | M, D, L, R                                                              | 2, 3            |              | ±60<br>±1200 |            |

| Power supply rejection ratio 4/        | PSRR              | $V_S = \pm 4V \text{ to } \pm 18V$ $V_S = \pm 4.5V \text{ to } \pm 18V$ | 1 2, 3          |              | 10           | μV/V       |

| Common mode rejection ratio 4/         | CMRR              | $V_{\text{CM}} = \pm 11 \text{V}$ $V_{\text{CM}} = \pm 10 \text{V}$     | 1 2, 3          | 114<br>108   | 10           | dB         |

| <u></u>                                |                   | $V_0 = \pm 10V, R_L = 2K\Omega$                                         | 4 5, 6          | 1000         |              |            |

| Large signal voltage gain              | $A_{VOL}$         | M, D, L, R                                                              | 4 4             | 500<br>800   |              | V/mV       |

| Input voltage range 4/                 | IVR               | $V_0 = \pm 10V, R_L = 600\Omega$                                        | 1               | ±11          |              | V          |

|                                        |                   | $RL = 2K\Omega$                                                         | 2, 3            | ±10<br>±12   |              |            |

| Output voltage swing 4/                | Vo                | RL = 600Ω                                                               | 5, 6<br>4       | ±11.5<br>±10 |              |            |

| Slew rate <u>2/</u> <u>4/</u>          | SR                | $RL = 2K\Omega$                                                         | 7               | 1.7          |              | V/µS       |

| Input noise voltage 4/                 | $e_N$             | $f_0 = 1 \text{ to } 100\text{Hz}$                                      | 7               |              | 50           | $nV_{RMS}$ |

| Gain bandwidth product 2/ 4/           | GBW               | f = 100kHz                                                              | 7               | 5.0          |              | MHz        |

| Input offset voltage match 4/          | Vos               |                                                                         | $\frac{1}{2,3}$ |              | 80<br>180    | μV         |

| Average non-inverting bias current 4/  | $I_B+$            | 3/                                                                      | 2, 3            |              | ±40<br>±60   | nA         |

| Non-inverting offset current 4/        | I <sub>os</sub> + | $I_{OS}$ + = $I_B$ +A - $I_B$ +B                                        | 1 2, 3          |              | ±60<br>±90   |            |

| Inverting offset current 4/            | I <sub>os</sub> - | $I_{OS} = I_{B} - A - I_{B} - B$                                        | 1 2, 3          |              | ±60<br>±90   |            |

## TABLE I NOTES:

$\frac{1}{2}$   $V_S = \pm 15V$ , unless otherwise specified  $\frac{2}{2}$  Guaranteed but not tested.

$$\frac{1}{2}$$

IB+= $\frac{(I_B + A) + (I_B + B)}{2}$

<u>4/</u> Not tested post irradiation.

## **4.1** Electrical Test Requirements:

| Table II                                |                                                         |  |  |  |

|-----------------------------------------|---------------------------------------------------------|--|--|--|

| Test Requirements                       | Subgroups (in accordance with MIL-PRF-38535, Table III) |  |  |  |

| Interim Electrical Parameters           | 1                                                       |  |  |  |

| Final Electrical Parameters             | 1, 2, 3, 4, 5, 6 <u>1/2/</u>                            |  |  |  |

| Group A Test Requirements               | 1, 2, 3, 4, 5, 6, 7                                     |  |  |  |

| Group C end-point electrical parameters | 1 <u>2/</u>                                             |  |  |  |

| Group D end-point electrical parameters | 1                                                       |  |  |  |

| Group E end-point electrical parameters | 1                                                       |  |  |  |

- 1/ PDA applies to Subgroup 1. Delta's excluded from PDA.

- 2/ See Table III for delta parameters. See table I for conditions.

## 4.2 Table III. Burn-in/Life Test delta limits.

|       |          | Table III |       |       |

|-------|----------|-----------|-------|-------|

| TEST  | BURN-IN  | GROUP C   | DELTA |       |

| TITLE | ENDPOINT | ENDPOINT  | LIMIT | UNITS |

| VOS   | ±80      | ±180      | ±100  | μV    |

| ±ΙΒ   | ±40      | ±50       | ±10   | nA    |

## 5.0 Life Test/Burn-In Circuit:

- 5.1 HTRB is not applicable for this drawing.

- 5.2 Burn-in is per MIL-STD-883 Method 1015 test condition B.

- 5.3 Steady state life test is per MIL-STD-883 Method 1005.

| Rev | Description of Change                                                           | Date          |

|-----|---------------------------------------------------------------------------------|---------------|

| A   | Initiate                                                                        | July 18, 2000 |

| В   | Update web address                                                              | Feb. 18, 2002 |

| C   | Add note 2 to TCVIO, Guaranteed if not tested, ref SMD 86887                    | Nov. 22, 2002 |

| D   | Update web address. Add note 4 to indicate parameters not test post irradiation | May 13, 2003  |

| Е   | Delete burn-in and radiation bias circuits                                      | Aug. 5, 2003  |

| F   | Add OP227-903M & OP227R903M versions                                            | Jul. 29, 2004 |

| G   | Update header/footer and add to 1.0 Scope description.                          | Feb. 25, 2008 |

|     |                                                                                 |               |

|     |                                                                                 |               |

|     |                                                                                 |               |