Search

Q

MY HISTORY | PARAMETRIC SEARCH | PRODUCTS | APPLICATIONS | DESIGN CENTER | COMMUNITY | EDUCATION | SUPPORT

Design Center > Evaluation Hardware & Software > JESD204 Interface Framework Design Center >

Evaluation Hardware & Software > JESD204 Interface Framework

Reference Designs

Hardware & Software

- | Evaluation (ACE) Software

- Evaluation Boards and Kits

- **Platforms**

- JESD204 Interface **Framework**

- Development **Platforms**

Packaging, Quality,

& Calculators

Processors & DSP

# JFSD204 Interface Framework

Integrated JESD204 software framework for rapid system-level development and optimization

Analog Devices' JESD204 Interface Framework is a system-level software and HDL package targeted at simplifying system development by providing a performance optimized IP framework that integrates complex hardware such as high speed converters, transceivers and clocks with various FPGA platforms.

The JESD204 Interface Framework provides an open platform that includes dynamic configuration capabilities to allow for system changes during operation and constraint handling to support built-in component models such as clocks and converters. These capabilities improve system-level integration and proof-of-concept testing leading to faster time-to-market.

## **Product Categories**

- A/D Converters

- D/A Converters

- RF & Microwave

- Clock & Timing

## Markets & Technology

- Aerospace and Defense

- Communications

- · Instrumentation and Measurement

#### Features and Benefits

- System level JESD204 framework designed for faster system integration

- Optimized software package for rapid prototyping and proof-of-concept testing

- HDL code interfaces JESD204 compliant converters and transceivers to FPGAs

- Dynamic configuration capabilities allow for system changes during operation

- · Constraint handling supports built-in component models and configures clocks and converters easing system integration

- Commercial and Open Source Licenses available:

#### · Additional features:

- Designed to JEDEC JESD204B specification

- Supports 1-256 Octets per frame and 1-32 frames per multi-frame

- Supports 1-32 lane configurations

- Supports line rates up to 12.5Gbps certified to the JESD204B specification

- Supports line rates up to 16.1Gbps

- Provides Physical and Data link layer functions

- AXI4-Stream interface for data

- AXI4-Lite for configuration interface

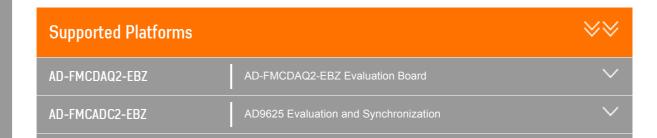

# Supported Platforms and Products

| AD-FMCADC3-EBZ     | ADA4961 & AD9625 Analog Signal Chain Evaluation and        | <b>~</b> |

|--------------------|------------------------------------------------------------|----------|

| AD-FMCADC4-EBZ     | ADA4961 & AD9680 Analog Signal Chain Evaluation and AD9528 | ~        |

| AD-FMCJESDADC1-EBZ | AD-FMCJESDADC1-EBZ Rapid Development Board                 | ~        |

| ADRV9371           | ADRV9371-N/PCBZ and ADRV9371-W/PCBZ Boards                 | ~        |

|                    |                                                            |          |

| A/D Converters |                                                                     | ** |

|----------------|---------------------------------------------------------------------|----|

| AD9680         | 14-Bit, 1.25 GSPS/1 GSPS/820 MSPS/500 MSPS<br>JESD204B, Dual Analog | ~  |

| AD9625         | 12-Bit, 2.6 GSPS/2.5 GSPS/2.0 GSPS, 1.3 V/2.5 V<br>Analog-to        | ~  |

| AD9250         | 14-Bit, 170 MSPS/250 MSPS, JESD204B, Dual<br>Analog-to-Digital      | ~  |

| AD6676         | Wideband IF Receiver Subsystem                                      | ~  |

| D/A Converters |                                                                | ** |

|----------------|----------------------------------------------------------------|----|

| AD9144         | Quad, 16-Bit, 2.8 GSPS, TxDAC+® Digital-to-Analog<br>Converter | ~  |

| AD9152         | Dual, 16-Bit, 2.25 GSPS, TxDAC+ Digital-to-Analog<br>Converter | ~  |

| AD9162         | 16-Bit, 12 GSPS, RF Digital-to-Analog Converters               | ~  |

| RF & Microwave |                                                       | <b>*</b> * |

|----------------|-------------------------------------------------------|------------|

| AD9371         | Integrated, Dual RF Transceiver with Observation Path | <b>~</b>   |

| Clock & Timing |                                                               | ** |

|----------------|---------------------------------------------------------------|----|

| AD9523-1       | Low Jitter Clock Generator with 14 LVPECL/LVDS/HSTL/29 LVCMOS | ~  |

# **Technical Resources**

## **Technical Articles**

- Synchronizing Sample Clocks of a Data Converter Array

- JESD204B Survival Guide PDF

## User Guides

JESD204 Interface Framework User Guide

WIKI

## Informational

• JESD204 Serial Interface

# **Buy Commercial License**

| Model         | License    | Price | Order    |

|---------------|------------|-------|----------|

| AD-IP-JESD204 | Commercial |       | Purchase |

# Support

Direct support is available for Commercial License holders. Contact your local ADI representative.

## **EngineerZone Support Communities**

Need Support? Visit more than 20 different product communities with thousands of separate discussions including FPGA.

15,000

**Problem Solvers**

4,700+

Patents Worldwide

125,000

50+

Years

# Ahead of What's Possible

Analog Devices is a global leader in the design and manufacturing of analog, mixed signal, and DSP integrated circuits to help solve the toughest engineering challenges.

See the Innovations

Analog Devices. Dedicated to solving the toughest engineering challenges.

## SOCIAL

## **QUICK LINKS**

About ADI **Analog Dialogue** Contact us **News Room**

Alliances Careers **Investor Relations Quality & Reliability** Sales & Distribution

#### **LANGUAGES**

English 简体中文 日本語 Русский

## **NEWSLETTERS**

Interested in the latest news and articles about ADI products, design tools, training and events? Choose from one of our 12 newsletters that match your product area of interest, delivered monthly or quarterly to your inbox.

Sign Up

© 1995 - 2018 Analog Devices, Inc. All Rights Reserved

Sitemap | Privacy & Security | Terms of use