### **USER GUIDE**

# **UG499: Si828x-AW-GDB Gate Driver Boards**

### 1. Introduction

The Si828x Gate Driver Boards (GDB) are ideal for driving Wolfspeed's XM3 1200 V Half Bridge Power Modules or other parallel combinations of discrete transistors. This two-channel isolated gate driver reference design in a half-bridge configuration features a differential digital interface, optimized on-board isolated power supply, DESAT protection, gate drive current boost, and user-configurable turn-on (RH) and turn-off (RL) gate resistors. Status indicator LEDs and test points make evaluation and prototyping easy.

## 1.1. Key Features

- Two digital gate drivers for high-side/low-side operation

- Up to +20 A, -30 A peak output current with integrated boost circuit

- Independent control of turn on/turn off timing through gate resistor selection

- Isolated power supplies

- 5 kVRMS safety rated isolation

- 125 kV/μs common mode transient immunity (CMTI)

- Reverse polarity protection for 12 V input supply

- Differential inputs for increased noise immunity

- DESAT detection and soft-shutdown for short-circuit protection

- Gate supply ready indicator

1

Module temperature (NTC) output as frequency modulated digital signal

## 1.2. Additional System Components

The Si828x GDB is highly versatile and can be combined with Wolfspeed's CIL boards and CGD12HB00D transceiver board to provide platforms to evaluate gate driver and SiC device combinations. The Si828x GDB is also designed to operate in Wolfspeed's 300kW Three-Phase Inverter platform, where three Si828x-AW-GDB provide all gate drivers necessary to drive the XM3 power modules.

Figure 1. Si828x Gate Driver Board (GDB)

September 19, 2022

### 1.3. Tested Components Include

- Evaluation Tool for the XM3 Module Platform

- CAB450M12XM3 Power Module

- Differential Transceiver Daughter Board

## 2. System Overview

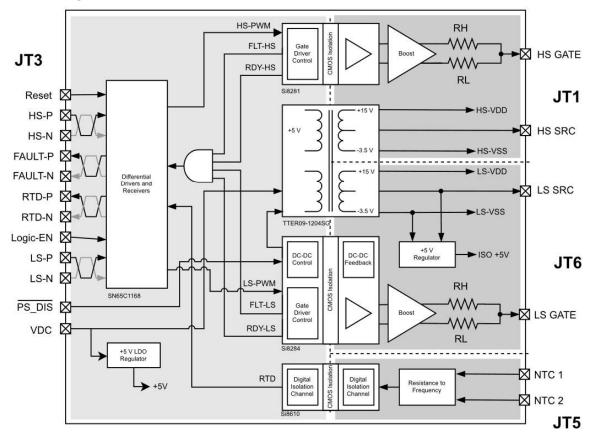

The Skyworks Si828x-AW-GDB is a printed circuit reference design suitable for interfacing to Wolfspeed XM3 power modules. The board contains isolated gate drive functions for high-side and low-side transistors in a half-bridge module configuration, with gate biasing, isolated power supply, and fault indication. Figure 2 provides a Si828x-AW-GDB functional diagram. The Si828x-AW-GDB is included in the Si828x-AAWB-GDB-KIT.

An I/O header (JT3) provides access to the differential high-side and low-side control signals as well as differential fault indicator outputs and temperature sensor outputs. It also exposes single-ended inputs for power supply disable, transceiver enable, and driver reset.

A digital transceiver converts the differential high-side and low-side PWM control signal inputs to the single-ended high-side and low-side gate drive control signals. The transceiver also converts a frequency-encoded NTC (Negative Temperature Coefficient) sensor output into a differential RTD signal and a single-ended signal representing the combined fault signals and ready signals from the high-side low-side gate drivers into a differential fault signal.

There are two gate drivers on the Si828x-AW-GDB. The low-side isolated gate drive is achieved by the Si8284x Isolated Gate Driver with Integrated DC-DC Converter. This device is driven by the single-ended low-side PWM signal and drives the gate of a switching device, either high or low by means of NPN and PNP transistors which provide enhanced drive current. A DESAT sensing pin provides a means of detecting switch desaturation and a soft shutdown circuit allows the switch to be shut down in a controlled manner if desaturation is detected. The circuit includes an enhanced Miller Clamp feature to ensure switch turn off is maintained in the presence of high slew rate drain/collector or source/emitter signals. Desaturation faults are indicated via the /FLT pin. Operation is restored by toggling the /RST pin via the Reset signal on the JT3 I/O header.

Loss of gate drive supply results in a loss of the RDY signal both on the RDY pin and the combined differential /FLT output at the header, but RDY is restored when the gate drive supply is restored.

The Si8284x also has a DC-DC controller function. This controller drives an external NMOS switch on the primary side of the power transformer. The secondary side of the transformer forms both high and low-side driver supplies. These supplies are +15 Vdc and -3.5 Vdc with a return between them and provide a total of 5 W between high and low-side sections. The high side supplies are isolated from the low side supplies by the transformer. The DC-DC controller function may be shut down via the PS-DISb input on the I/O header.

High-side isolated gate drive is achieved by the Si8285 Isolated Gate Driver. This device and its associated circuit provide the same function as the Si8284 but without the DC-DC controller.

The DC power input to the board is protected from a reverse polarity connection via the P channel MOSFET gate biasing voltage UB2.

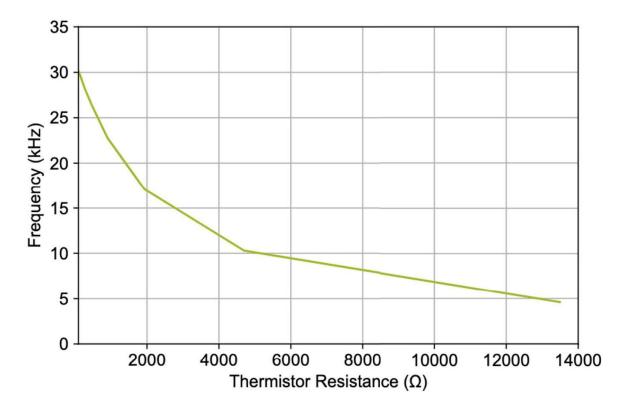

An RTD connector provides the connection to an external NTC (negative temperature coefficient) resistive sensor for measurement of switch module temperature. The RTD resistance is converted to a frequency that is then isolated and sent to the differential transceiver, which is converted to a differential signal accessed via the I/O header.

The AN1362: Si828x XM3 Gate Driver Test Report provides more detailed information and a complete schematic of the Si828x-AW-GDB. It also includes test setup and performance data of the operations between the Si828x gate driver and the XM3 SiC module on the Evaluation Tool for the XM3 Module Platform.

### **Function Block Diagram**

Figure 2. Function Block Diagram

# 3. Pin Descriptions

# 3.1. Input I/O Connector (Low-Voltage JT3)

This connector is located in the center of the Si828x-AW-GDB. In the **XM3 Evaluation Tool** test setup, the JT3 connector provides the I/O interface connections across the **Differential Transceiver Daughter Board Companion Tool** to the lab bench instrumentations including power supply, function generator, control signals, etc. In the **XM3 Inverter Reference Design**, the JT3 connector provides direction connection to the controll board, enabling the evaluation of the Si828x-AW-GDB in high power inverter applications. Table 1 provides a complete list of the signals in the JT3 connector.

| Pin Number                                     | Parameter | Description                                                                                                                                                                                                                          |  |

|------------------------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1                                              | VDC       | Power supply input pin (+12 V Nominal Input)                                                                                                                                                                                         |  |

| 2                                              | Common    | Common                                                                                                                                                                                                                               |  |

| 3                                              | HS-P      | Positive line of 5 V differential high-side PWM signal pair. Terminated Into 120 Ω                                                                                                                                                   |  |

| 4                                              | HS-N      | Negative line of 5 V differential high-side PWM signal pair. Terminated into $120\Omega$                                                                                                                                             |  |

| 5                                              | LS-P      | Positive line of 5 V differential low-side PWM signal pair. Terminated into 120 $\Omega$                                                                                                                                             |  |

| 6                                              | LS-N      | Negative line of 5 V differential low-side PWM signal pair. Terminated into 120 Ω                                                                                                                                                    |  |

| 7                                              | FAULT- P  | Positive line of 5 V differential fault condition signal pair. Drive strength 20 mA. A low state on FAULT indicates when a desaturation fault has occurred. The presence of a fault precludes the gate drive output from going high. |  |

| 8                                              | FAULT- N  | Negative line of 5 V differential fault condition signal pair. Drive strength 20 mA. A low state on FAULT indicates when a desaturation fault has occurred. The presence of a fault precludes the gate drive output from going high. |  |

| 9                                              | RTD-P     | Positive line of 5 V temperature dependent resistor output signal pair. Drive strength 20 mA. Temperature measurement is encoded via frequency.                                                                                      |  |

| 10                                             | RTD-N     | Negative line of 5 V temperature dependent resistor output signal pair. Drive strength 20mA. Temperature measurement is encoded via frequency.                                                                                       |  |

| 11                                             | PS-DIS    | Pull down to disable power supply. Pull up or leave floating to enable. Gate and source are connected with 10 k $\Omega$ when disabled.                                                                                              |  |

| 12                                             | Common    | Common                                                                                                                                                                                                                               |  |

| 13                                             | PWM EN    | Pull down to disable PWM input logic. Pull up or leave floating to enable. Gate driver output will be held low through turn-off gate resistor if power supplies are enabled.                                                         |  |

| 14                                             | Common    | Common                                                                                                                                                                                                                               |  |

| 15                                             | RESET     | When a fault exists, bring this pin high to clear the fault.                                                                                                                                                                         |  |

| 16                                             | Common    | Common                                                                                                                                                                                                                               |  |

| Note:<br>Inputs 3 to 10 are differential pair. |           |                                                                                                                                                                                                                                      |  |

Table 1: Input I/O Connector (Low Voltage JT3)

- **PWM Signals:** High-side and low-side PWM are RS-422 compatible differential inputs. The termination impedance of the differential receiver is 120 Ω.

- **FAULT Signal:** The fault signal is an RS-422 compatible differential output with a maximum drive strength of 20mA. A high signal (positive line > negative line) means there are no fault conditions for either gate driver channel. This signal will be low if an overcurrent fault or UVLO fault condition is detected on either channel. A red LED will indicate a fault condition. The LED, DT6, indicates a high-side fault and DT8 indicates a low-side fault.

- **UVLO Fault:** The UVLO circuit detects when the output rails of the isolated DC/DC converter fall below safe operating conditions for the gate driver. A UVLO fault indicates that the potential between the split output rails has fallen below the UVLO active level. The gate for the channel where the fault occurred will be pulled low through RG for the duration of the fault regardless of the PWM input signal. The fault will automatically clear once the potential has risen above the UVLO inactive level. There is hysteresis for this fault to ensure safe operating conditions. The UVLO faults for both channels are combined along with the over-current fault in the FAULT output signal. When there is no UVLO fault present, a green LED indicates a power good state. The LED, DT5, indicates a high-side power good status and DT7 indicates a low-side power good status.

- Over-Current Fault: An over-current fault is an indication of an over-current event in the SiC power module. The overcurrent protection circuit measures the drain-source voltage, and the fault will indicate if this voltage has risen above a level corresponding to the safe current limit. When a fault has occurred the corresponding gate driver channel will be disabled, and the gate will be pulled down through a soft-shutdown resistor, RSS. The drain-source limit can be configured through on-board resistors. The over-current fault is latched upon detection and must be cleared by the user with a high pulse of at least 500 ns on the RESET signal.

- RTD (NTC): RTD output is a differential signal that returns the resistance of the temperature sensor (NTC) integrated into XM3 modules. The signal is a frequency modulated signal that encodes the resistance of the temperature sensor. The approximate temperature of the module can be determined from this resistance. See the section RTD (NTC) Temperature Feedback for further details.

- **PS-DISb:** The PS-DISb signal disables the output of the isolated DC/DC converters for the two channels. It is a single-ended input that must be pulled low to turn off the power supplies. With the power supplies disabled the gate will be held low with a 10 k $\Omega$  resistor. This signal can be used for startup sequencing.

- **PWM-EN:** This is a single-ended input that enables the PWM inputs for both channels. When this signal is pulled down the differential receivers for both channels are disabled and the gates will both be pulled low through R\_G-OFF. All protection circuitry and power supplies will continue to operate including FAULT and RTD outputs.

- **RESET:** This single-ended input clears a desaturation-induced fault state, allowing PWM inputs to function as soon as RESET is released. When the signal is set high, FAULT will assume a high state if there are no UVLO conditions. The signal should be returned to low in order to operate the device.

- Over-Voltage and Reverse Polarity Protection: Power input on pin 1 is protected against connecting a power source with over-voltage or reverse polarity; there is a diode and a Zener diode across the power input, and a MOSFET in-line with the power input.

## 3.2. Module Connectors (High-Voltage)

These connectors are located at the bottom of the Si828x-AW-GDB and provide direct connections to the Wolfspeed XM3 SiC half-bridge modules. Table 2 provides a listing and locations of the signals on the module connectors.

| Connector<br>Reference | Parallel<br>Connector Pins<br>Si828x-AW-GDB | Signal Name          | Description                                            |

|------------------------|---------------------------------------------|----------------------|--------------------------------------------------------|

| JT1                    | 2, 4                                        | HS-Gate              | High-side gate lead of switch module                   |

| JT1                    | 1, 3                                        | HS-Source (LS-Drain) | High-side source lead of switch module; primary output |

| JT2                    | 1, 2, 3, 4                                  | HS-Drain             | High-side drain lead of switch module                  |

| JT6                    | 2, 4                                        | LS-Gate              | Low-side gate lead of switch module                    |

| JT6                    | 1, 3                                        | LS-Source            | Low-side source lead of switch module                  |

| JT5                    | 1, 3                                        | RTD-1                | Lead 1 of switch module resistive temperature sensor   |

| JT5                    | 2, 4                                        | RTD-2                | Lead 2 of switch module resistive temperature sensor   |

**Table 2: Module Connectors (High Voltage)**

- **HS-Gate:** The high-side gate pin is driven by the Si8281 Isolated Gate Driver IC and external BOM circuitry meant to enhance the drive, soft shutdown, and Miller clamp functions for higher gate capacitance switch devices / arrays.

- **HS-Source:** The high-side source pin is connected to the VMID-H supply and the low-side DESAT detection circuit.

- **HS-Drain:** The high-side drain pin is connected to the high-side DESAT detection circuit.

- **LS-Gate:** The low-side gate pin is driven by the Si8285 Isolated Gate Driver IC and external BOM circuitry meant to enhance the drive, soft shutdown, and Miller clamp functions for higher gate capacitance switch devices / arrays.

- LS-Source: The low-side source pin is connected to the VMID-L supply.

- RTD-1 and RTD-2: The RTD pins connect to a resistive temperature sensor in the switch device / module. The resistance is sensed and converted to a frequency which is then sent across an isolation barrier to the digital transceiver and out the I/O connector.

5

## 4. Truth Table

Table 3 provides the truth table of the input to output signals under various operating conditions.

Table 3: Si828x-AW-GDB I/O Truth Table

| HS-PWM | LS-PWM | PWM-EN <sup>2</sup> | PS-DIS <sup>4</sup> | Reset_Input <sup>3</sup> | Overcurrent UVLO | FAULT <sup>8</sup> | HS-Gate        | LS-Gate        | Output<br>(HS-Source/LS-Drain) |

|--------|--------|---------------------|---------------------|--------------------------|------------------|--------------------|----------------|----------------|--------------------------------|

| L      | L      | H or Z              | H or Z              | L or Z                   | No               | Н                  | L              | L              | Z                              |

| L      | Н      | H or Z              | H or Z              | L or Z                   | No               | Н                  | L              | Н              | L                              |

| Н      | L      | H or Z              | H or Z              | L or Z                   | No               | Н                  | Н              | L              | Н                              |

| Н      | Н      | H or Z              | H or Z              | L or Z                   | Yes <sup>5</sup> | L                  | H <sup>9</sup> | H <sup>9</sup> | Z <sup>9</sup>                 |

| Х      | Х      | L <sup>6</sup>      | H or Z              | L or Z                   | No               | Н                  | L              | L              | L                              |

| Х      | Х      | Х                   | L7                  | Х                        | No               | L                  | L              | L              | Z                              |

| Х      | Х      | H or Z              | H or Z              | L or Z                   | Yes              | L                  | L              | L              | Z <sup>9</sup>                 |

#### Notes:

- 1. H = High | L = Low | X = Irrelevant | Z = High Impedance

- 2. PWM-EN is active high and has a pull up resistor on the input.

- 3. Reset\_Input is active high and has a pull down resistor on the input.

- 4. PS-DIS\ is active low and has a pull up resistor on the input.

- 5. An Overcurrent condition is induced when both PWM inputs are high. This condition must be disallowed by external overlap protection.

- 6. A low on PWM-EN disables the outputs of the PWM receivers; they are pulled low by resistors in this case.

- 7. When PS-DIS\ is low, the gate driver output power supply is disabled. The HS-Gate and LS-Gate signals are pulled to their respective sources by resistors.

- 8. The FAULT output is active low; it goes low when there is an overcurrent / UVLO fault or a driver IC indicates a non-READY state.

- 9. When an overcurrent condition is induced, the gate signals are pulled low and the output becomes high-impedance after the fault condition is indicated by a driver chip.

## 5. Gate Driver Connections

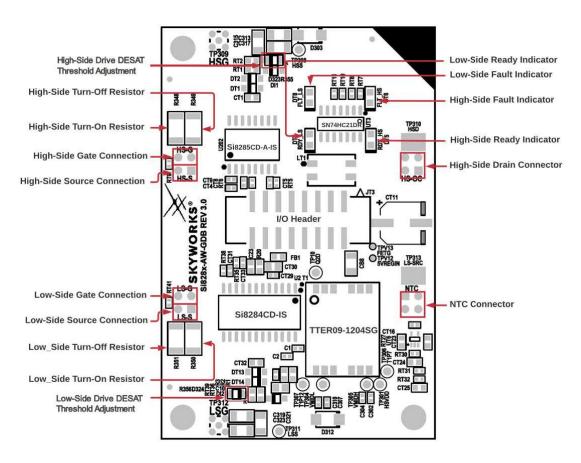

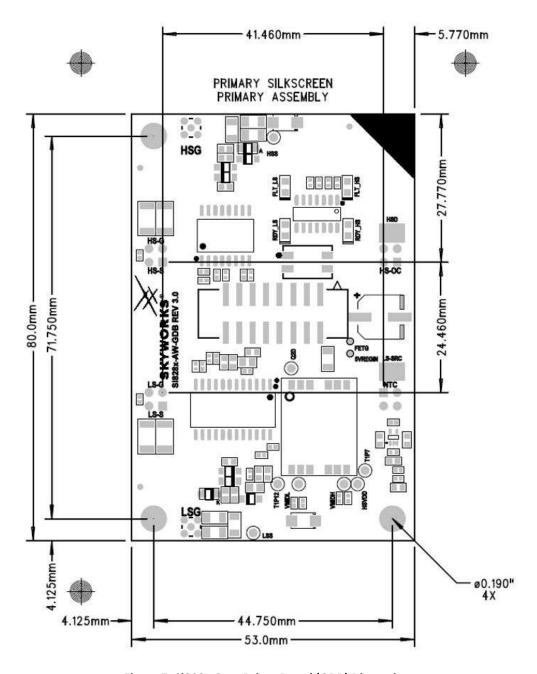

Figure 3. Si828x Gate Driver Board Top-Side Silkscreen

# 6. Temperature Feedback

The XM3 power module uses a thermistor to provide temperature feedback to the controller. The resistance of the thermistor sensor is converted to a 50% duty cycle square wave with a frequency that varies inversely with the resistance. The resistance to frequency relationship is displayed in the Table 4 below. The resistance to frequency circuits is located on the high voltage side to provide direct connection to the XM3 thermistor sensor. Then, a digital isolator is used to transmit the frequency-encoded signal back to the primary side and its differential signals are connected to pin 9 and pin 10 of the JT3 low side connector.

Figure 4. Thermistor Resistance vs Output Frequency

**Table 4: Thermistor Resistance vs Output Frequency**

| Thermistor Resistance (Ω) | Frequency Output (kHz) |

|---------------------------|------------------------|

| 13491                     | 4.6                    |

| 4700                      | 10.3                   |

| 1928                      | 17.1                   |

| 898                       | 22.8                   |

| 464                       | 26.4                   |

| 260                       | 28.3                   |

| 156                       | 29.5                   |

| 99                        | 30.1                   |

# 7. User Configuration Options

### 7.1. Series Gate Resistors

The Si828x GDB has 1  $\Omega$  series gate resistors in series with the gate drive signal for both the high side and the low side channels. In addition, these resistor values are the same for both turn on (RG-ON) and turn off (RG-OFF).

However, the user can select any value for turn-on and turn off timing control independently. Resistors R348 and R350 control the turn-on timing for the high side and low side channels respectively. Resistors R349 and R51 affect the turn-off time for the high side and low side respectively. This configuration provides the user with complete flexibility in tuning the turn-on and turn-off times for each channel.

### 7.2. Negative Gate Bias

The default configuration of this driver board provides a gate drive signal that swings from +15 V to -3.7 V with respect to the source pin connection.

### 7.3. Isolated Driver Power Supply Voltage

The Si828x GDB uses a dc-dc converter integrated into the Si8284 gate driver. This converter regulates the output of one secondary of the transformer used in the application. The design of the transformer provides regulation of the other secondary winding to provide separate, isolated power supplies for both the high side and low side driver. The default configuration provides a driver power supply that is regulated to 19 V. Since the source pin of each channel is biased about 3.6 V above the converter's reference, the gate will see a voltage swing from +15 V to -4 V when measured with respect to the source pin.

The DC-DC converter may be operated with a different set of output voltages by changing the resistor divider (R1/R2+1) \* 1.05V to obtain the desired supply voltage. The limit of VDDB - VSSB is 30V, and the VDDB/VSSB ratio is fixed by the turns ratios of transformer T1. Operating the device at a higher voltage may impair operation or damage the device.

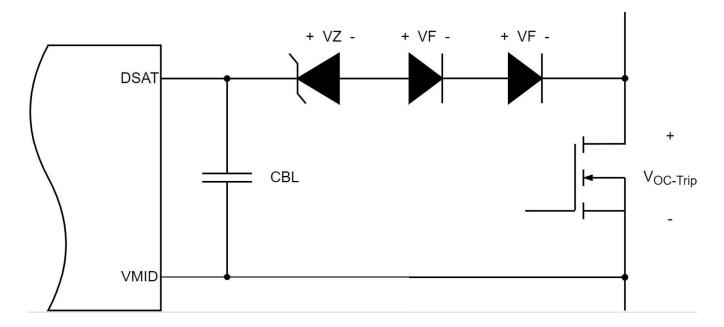

### 7.4. Overcurrent/Desaturation Trip Level

The overcurrent (OC) fault detection circuit measures the on-state VDS voltage across each switch position and triggers a fault condition if the voltage rises above a set level. The internal comparator trip voltage in the Si828x gate driver IC is 7 V. Considering the forward voltage of the high-voltage blocking diodes and a tunable Zener diode, the overcurrent trip level is calculated with the following equation:

VOC-Trip = 7V - VZ - 2VF

where the forward voltage of the high-voltage diodes, VF, is approximately 0.5 V, and the Zener voltage, VZ, included on the gate driver is 3.9 V (On Semi MMSZ4686T1G). As shipped, the Zener diode is replaced with a 0 Ohm resistor and the overcurrent trip level is 6 V. If it is desired to change the overcurrent trip level, the Zener diode should be in a SOD123 package such as the diodes in the MMSZ series from On Semi. The Zener diodes are labeled D323 and D324 on the PCB.

Figure 5. Over-Current Trip Level

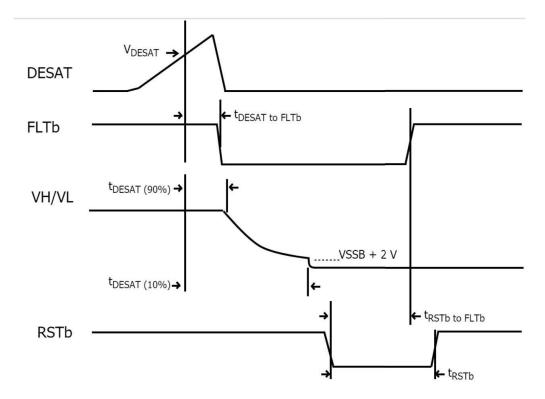

Figure 6. DESAT Behavior

To set an appropriate overcurrent trip level, see the module data sheet for the ID vs. VDS output characteristic curves. For example, the pulse-current rating of the CAB450M12XM3 is 900 A at TJ = 25 °C; it follows that an overcurrent trip point of 1000 A at 25 °C should be selected. The drain-to-source voltage at the 1000 A operating condition is approximately 3.0 V, as seen on the ID vs. VDS curve. From that, the overcurrent trip voltage, VOC-Trip, should be approximately 3.0 V. This trip voltage can be used to calculate the required Zener voltage, VZ, with the equation above.

Note that the HS-Drain connector, JT2, cannot be left floating because the over-current fault will trip immediately when the high-side gate is taken high. If bench testing of the gate driver is required without the XM3 module, one may short the HS-Drain connection to the high-side source to prevent the overcurrent fault from tripping. The low-side exhibits the same behavior, and one may short the high-side source (low-side drain) to the low-side source for bench testing. The Reset signal must be activated to acknowledge the over-current fault condition so as to return the gate driver to normal operation.

### 7.5. Si828x-AW-GDB - XM3 Test Circuits

The Si828x-AW-GDB is designed to operate with Wolfspeed's XM3 Evaluation Tool and the XM3 Three-Phase Inverter Demonstration Platform. The Si828x-AW-GDB was tested extensively with the XM3 module on the Wolfspeed's XM3 Evaluation Tool with excellent test results. The Si828x-AW-GDB fits directly to the gate driver slots of the XM3 Three Phase Demonstration Platform. Below are the links to the documentation for test setup and test results.

Si828x-XM3 Test Report: AN1362

XM3 Evaluation Tool: KIT-CRD-CIL12N-XM3

Differential Transceiver Daughter Board

XM3 Three-Phase Inverter Reference Design User Guide: AN30

# 8. Dimensions

Figure 7. Si828x Gate Driver Board (GDB) Dimensions

# **Ordering Information**

| Part Number     | Part Description                                                           |  |  |

|-----------------|----------------------------------------------------------------------------|--|--|

| Si828x-AAWB-KIT | KIT contains the Si828x-AW-GDB evaluation board described in this document |  |  |

Copyright © 2022, Skyworks Solutions, Inc. All Rights Reserved.

Information in this document is provided in connection with Skyworks Solutions, Inc. ("Skyworks") products or services. These materials, including the information contained herein, are provided by Skyworks as a service to its customers and may be used for informational purposes only by the customer. Skyworks assumes no responsibility for errors or omissions in these materials or the information contained herein. Skyworks may change its documentation, products, services, specifications or product descriptions at any time, without notice. Skyworks makes no commitment to update the materials or information and shall have no responsibility whatsoever for conflicts, incompatibilities, or other difficulties arising from any future changes.

No license, whether express, implied, by estoppel or otherwise, is granted to any intellectual property rights by this document. Skyworks assumes no liability for any materials, products or information provided hereunder, including the sale, distribution, reproduction or use of Skyworks products, information or materials, except as may be provided in Skyworks' Terms and Conditions of Sale.

THE MATERIALS, PRODUCTS AND INFORMATION ARE PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND, WHETHER EXPRESS, IMPLIED, STATUTORY, OR OTHERWISE, INCLUDING FITNESS FOR A PARTICULAR PURPOSE OR USE, MERCHANTABILITY, PERFORMANCE, QUALITY OR NON-INFRINGEMENT OF ANY INTELLECTUAL PROPERTY RIGHT; ALL SUCH WARRANTIES ARE HEREBY EXPRESSLY DISCLAIMED. SKYWORKS DOES NOT WARRANT THE ACCURACY OR COMPLETENESS OF THE INFORMATION, TEXT, GRAPHICS OR OTHER ITEMS CONTAINED WITHIN THESE MATERIALS. SKYWORKS SHALL NOT BE LIABLE FOR ANY DAMAGES, INCLUDING BUT NOT LIMITED TO ANY SPECIAL, INDIRECT, INCIDENTAL, STATUTORY, OR CONSEQUENTIAL DAMAGES, INCLUDING WITHOUT LIMITATION, LOST REVENUES OR LOST PROFITS THAT MAY RESULT FROM THE USE OF THE MATERIALS OR INFORMATION, WHETHER OR NOT THE RECIPIENT OF MATERIALS HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

Skyworks products are not intended for use in medical, lifesaving or life-sustaining applications, or other equipment in which the failure of the Skyworks products could lead to personal injury, death, physical or environmental damage. Skyworks customers using or selling Skyworks products for use in such applications do so at their own risk and agree to fully indemnify Skyworks for any damages resulting from such improper use or sale.

Customers are responsible for their products and applications using Skyworks products, which may deviate from published specifications as a result of design defects, errors, or operation of products outside of published parameters or design specifications. Customers should include design and operating safeguards to minimize these and other risks. Skyworks assumes no liability for applications assistance, customer product design, or damage to any equipment resulting from the use of Skyworks products outside of Skyworks' published specifications or parameters.

Skyworks, the Skyworks symbol, Sky5°, SkyOne°, SkyBlue™, Skyworks Green™, ClockBuilder°, DSPLL°, ISOmodem°, ProSLIC°, and SiPHY° are trademarks or registered trademarks of Skyworks Solutions, Inc. or its subsidiaries in the United States and other countries. Third-party brands and names are for identification purposes only and are the property of their respective owners. Additional information, including relevant terms and conditions, posted at www.skyworksinc.com, are incorporated by reference.